System Register Block

UG0331 User Guide Revision 15.0 696

Note: Do not change these register fields dynamically for 005 and 010 devices, see System Registers Behavior

for M2S005/010 Devices, page 682.

22.3.23 Loopback Control Register

Note: Do not change these register fields dynamically for 005 and 010 devices, see System Registers Behavior

for M2S005/010 Devices, page 682.

22.3.24 GPIO System Reset Control Register

1 FAB1_AHB_BYPASS 0 0: FIC_1 is configured for synchronous bridging

1: FIC_1 is configured in bypass mode, if clock ratio is 1:1 and if in

AHB mode

0 FAB0_AHB_BYPASS 0 0: FIC_0 is configured for synchronous bridging

1: FIC_0 is configured in bypass mode, if clock ratio is 1:1 and if in

AHB mode

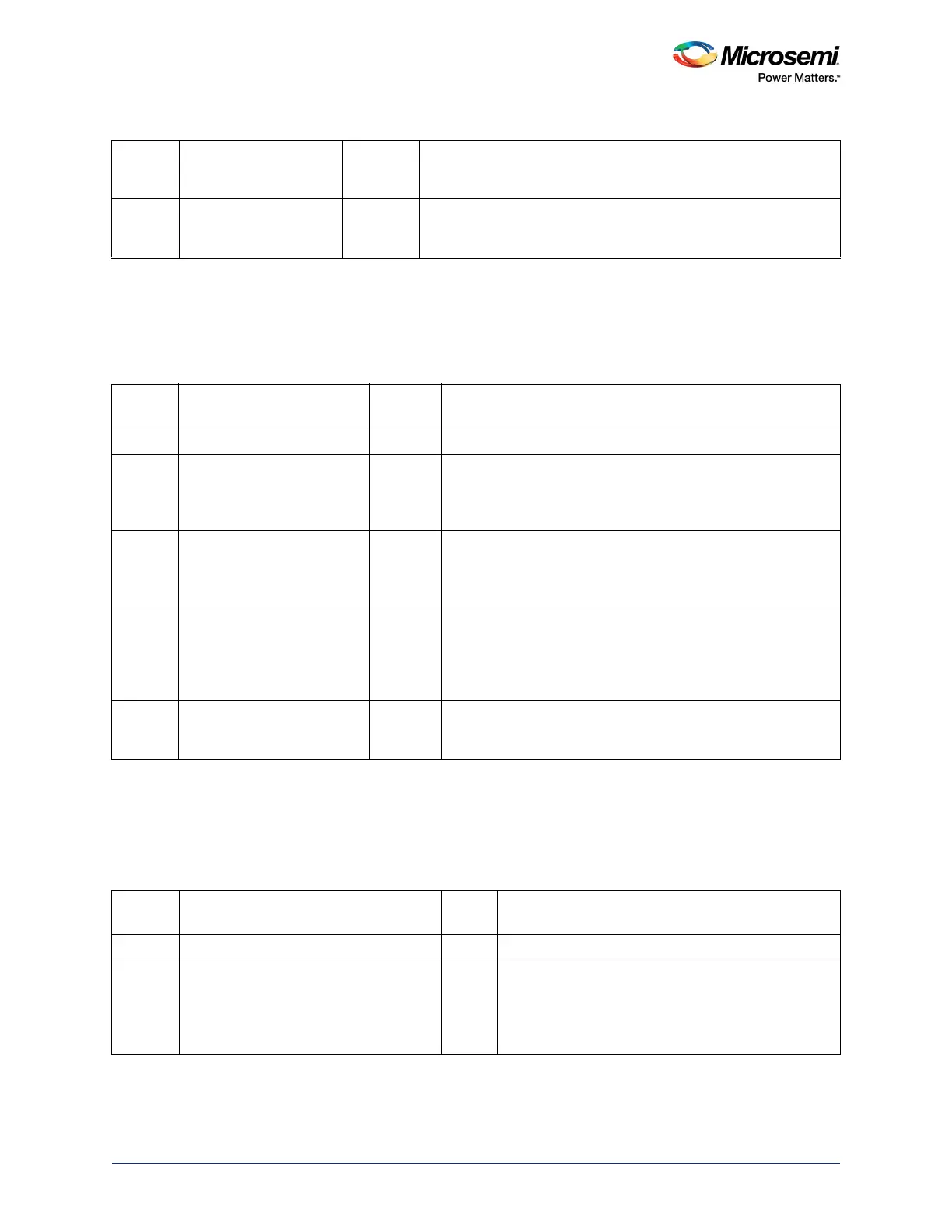

Table 677 • LOOPBACK_CR

Bit

Number Name

Reset

Value Description

[31:4] Reserved 0

3 MSS_GPIOLOOPBACK 0 Controls whether internal loopback on the MSS GPIO is

enabled. Allowed values:

0: No internal loopback

1: MSS GPIO outputs are looped back to MSS GPIO inputs

2 MSS_I2CLOOPBACK 0 Controls whether internal loopback between I2C_0 and I2C_1 is

enabled. Allowed values:

0: No internal loopback

1: Traffic from I2C_0 is looped back to I2C_ and vice versa

1 MSS_SPILOOPBACK 0 Controls whether internal loopback between SPI_0 and SPI_1

is enabled. Allowed values:

0: No loopback

1: SPI_0 Tx is looped back to SPI_1 Rx. SPI_1 Tx is looped

back to SPI_0 Rx

0 MSS_MMUARTLOOPBACK 0 0: No loopback between MMUART_0 and MMUART_1

1: MMUART_0 Tx is looped back to MMUART_1 Rx

MMUART_1 Tx is looped back to MMUART_0 Rx

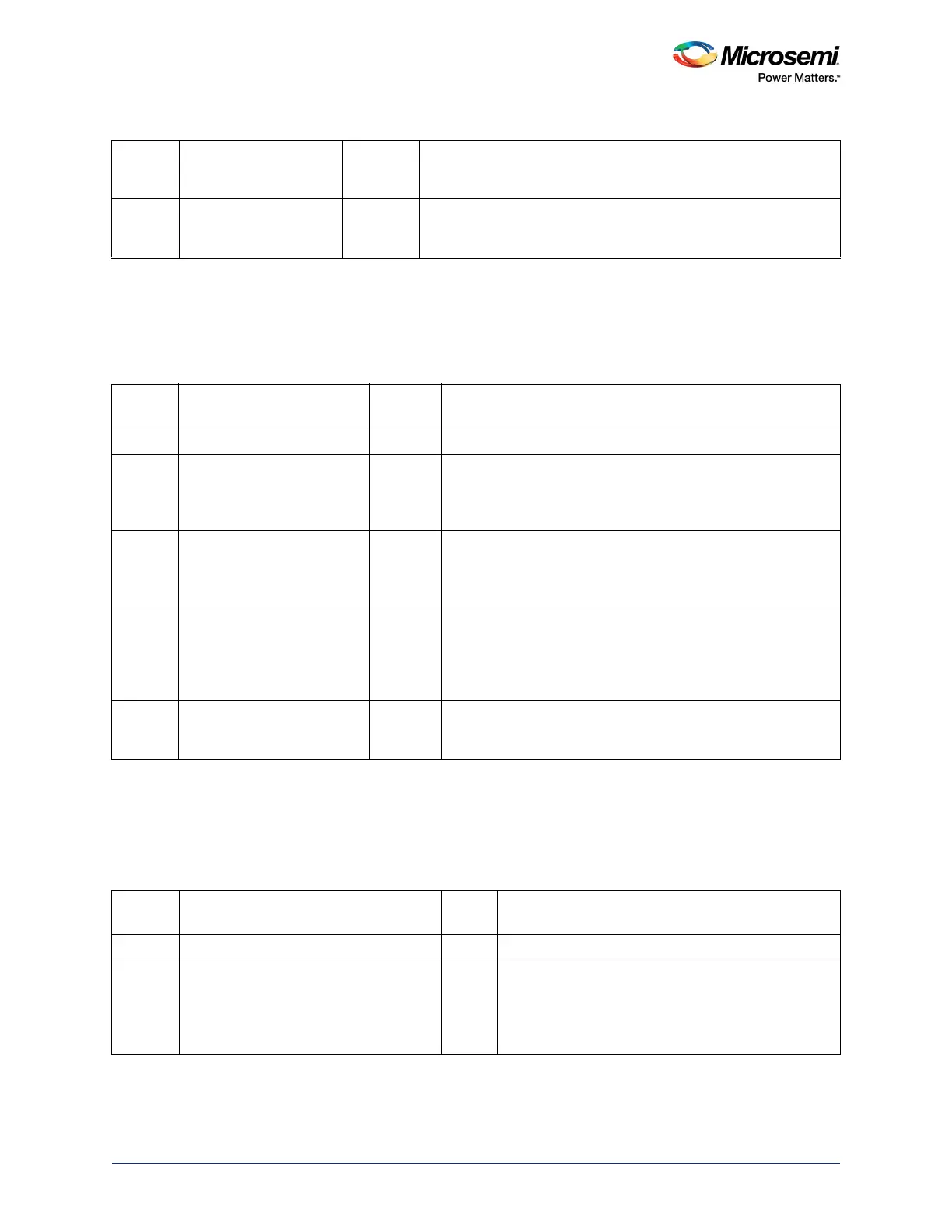

Table 678 • GPIO_SYSRESET_SEL_CR

Bit

Number Name

Reset

Value Description

[31:4] Reserved 0

3 MSS_GPIO_31_24_SYSRESET_SEL 0 0: Selects the combination of either

power-on reset or the MSS_GPIO_RESET_N signal

from the FPGA fabric to reset the GPIO

1: Causes GPIO[31:24] to be held in reset by the soft

reset signal MSS_GPIO_31_24_SOFT_RESET

Table 676 • FAB_IF_CR (continued)

Loading...

Loading...