Cortex-M3 Processor (Reference Material)

UG0331 User Guide Revision 15.0 103

3.7.2.3 Interrupt Control and State Register

The ICSR:

• Provides:

• a set-pending bit for the Non-Maskable Interrupt (NMI) exception

• set-pending and clear-pending bits for the PendSV and SysTick exceptions

• Indicates:

• the exception number of the exception being processed

• whether there are preempted active exceptions

• the exception number of the highest priority pending exception

• whether any interrupts are pending.

See the register summary in Table 50, page 102, and the Type descriptions in the following table, for the

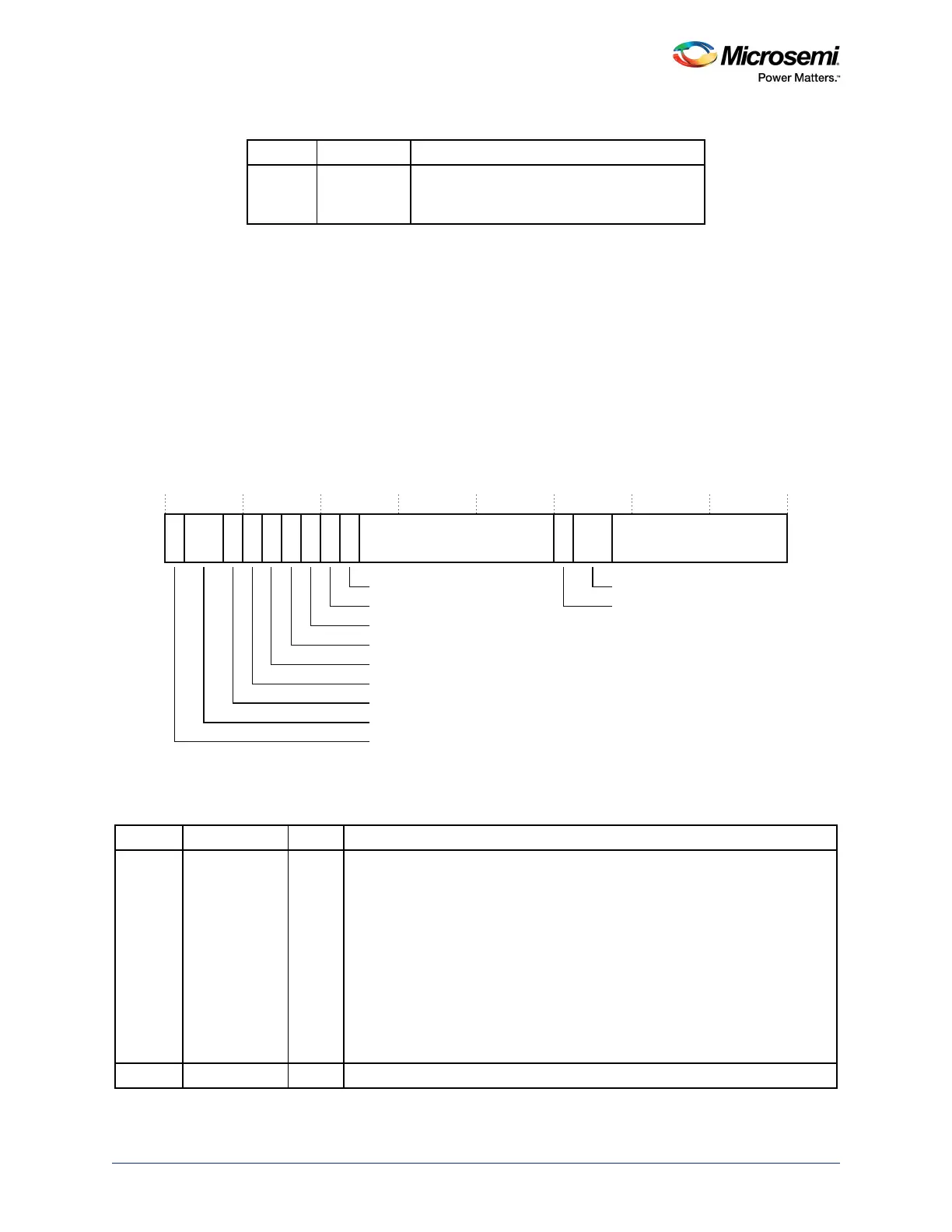

ICSR attributes. The bit assignments are:

Figure 32 • ICSR Bit Assignments

[3:0] Revision Revision number, the p value in the rnpn

product revision identifier:

0x0 = Patch 0

Table 53 • ICSR Bit Assignments

Bits Name Type Function

[31] NMIPENDSET RW NMI set-pending bit.

Write:

0: no effect

1: changes NMI exception state to pending.

Read:

0: NMI exception is not pending

1: NMI exception is pending.

Because NMI is the highest-priority exception, normally the processor enter the

NMI exception handler as soon as it registers a write of 1 to this bit, and

entering the handler clears this bit to 0. A read of this bit by the NMI exception

handler returns 1 only if the NMI signal is reasserted while the processor is

executing that handler.

[30:29] Reserved.

Table 52 • CPUID register Bit Assignments (continued)

Bits Name Function

31 28 22 21 910 0

VECTACTIVE

30 29 27 26 2324 12 11

VECTPENDING

NMIPENDSET

PENDSVSET

PENDSVCLR

Reserved for Debug

ISRPENDING Reserved

RETTOBASE

25

PENDSTSET

PENDSTCLR

8

Reserved

Reserved

Loading...

Loading...