Serial Peripheral Interface Controller

UG0331 User Guide Revision 15.0 506

SPI_X_TXRFM (SPI has room for more data to send) ports. These are connected to the peripheral DMA

(PDMA) engine to allow continuous DMA streaming for large SPI transfers and to help free up the

Cortex-M3 processor.

14.2.1.2 Configuration and Control Logic

The SPI peripheral can be configured for master or slave mode by using the mode bit of the SPI

CONTROL register. The type of data transfer protocol can be configured by using the TRANSFPRTL bit

of the SPI CONTROL register. The control logic monitors the number of data frames to be sent/received

and enables the interrupts when the data frame transmission/reception is completed. During data frames

transmission/reception, if a transmit under-run error/receive overflow error is detected, the Status register

is updated (refer to the STAT8 register for bit definitions).

14.2.1.3 SPI Clock Generator

In master mode, the SPI clock generator generates the serial programmable clock from the APB clock.

Refer to the SPI Clock Requirements, page 517 for more details.

14.2.2 Interface

This section provides the details of the SPI interfacing ports and various data transfer protocols.

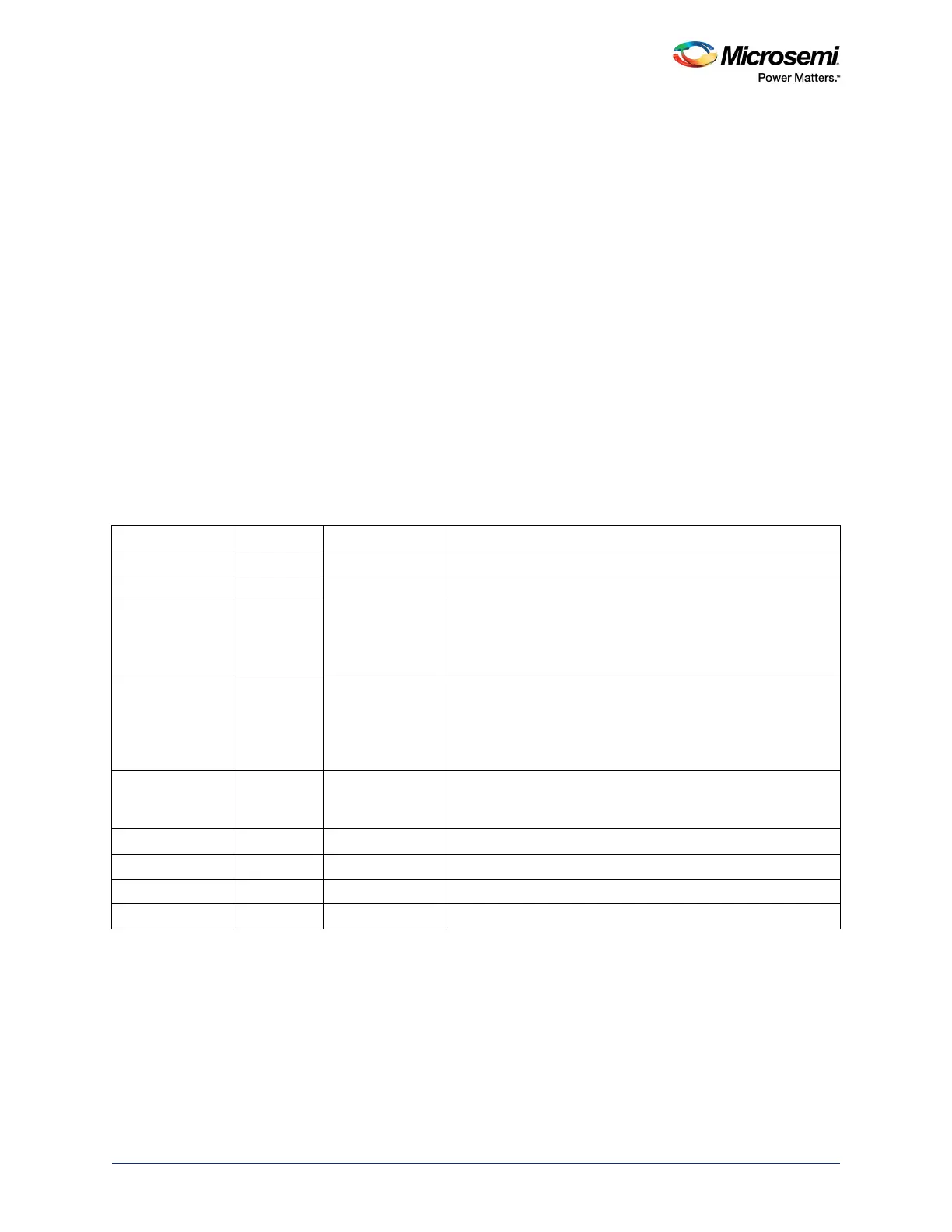

14.2.2.1 Port List

The following table lists the SPI signals.

14.2.2.2 Data Transfer Protocol Details

The SmartFusion2 SPI controller supports the following data transfer protocols:

• Motorola SPI Protocol

• National Semiconductor MICROWIRE Protocol

• Texas Instruments Synchronous Serial Protocol

• Slave Protocol Engine

This section describes the data transfer protocols, timing diagrams, signal requirements, and error case

scenarios for the above protocols.

Table 492 • SPI Interface Signals

Name Type Polarity Description

SPI_X_DI Input High Serial data input

SPI_X_DO Output High Serial data input

SPI_X_CLK Input/Output High Serial clock. It is a serial programmable bit rate clock out

signal.

Input when SPI is in the slave mode.

Output when SPI is in the master mode.

SPI_X_SS[0] Input/Output Low,

except for TI mode

Slave select.

Input when SPI is in the slave mode.

Output when SPI is in the master mode.

The slave select output polarity is active Low. In TI mode the

slave select output is inverted to become active High.

SPI_X_SS[7:1] Output Low,

except for TI mode

Extra slave select signal. Valid only in the Master mode.

The slave select output polarity is active Low. In TI mode the

slave select output is inverted to become active High.

SPI_X_INT Output High SPI interrupt

SPI_X_DOE_N Output High Output enable

SPI_X_TXRFM Output High SPI ready to transmit. Used only by MSS PDMA engine

SPI_X_RXAVAIL Output High SPI received data. Used only by MSS PDMA engine.

Loading...

Loading...