Reset Controller

UG0331 User Guide Revision 15.0 656

• Instrumentation trace macrocell (ITM)

•AHB-AP

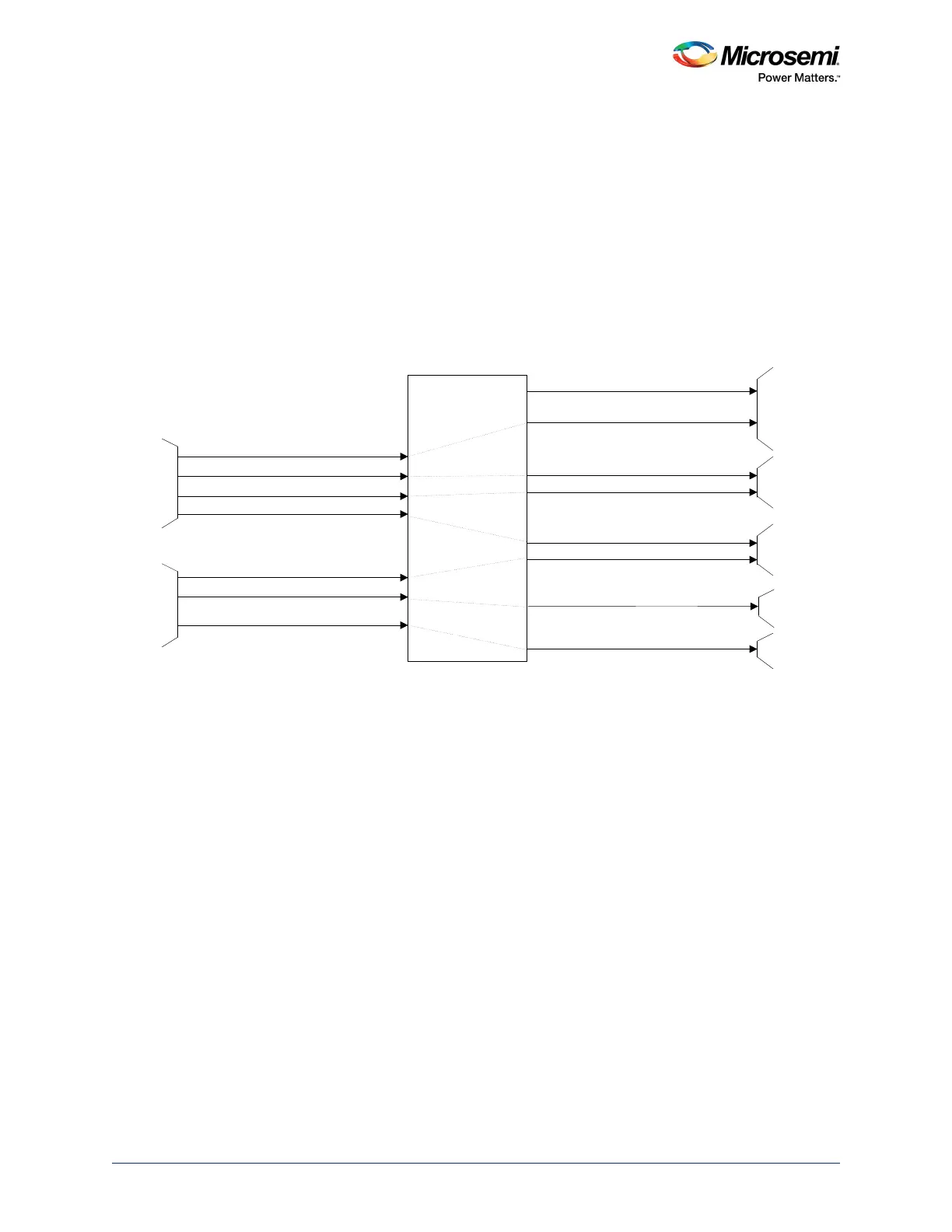

21.2.6 Block Resets

The Reset Controller generates block level resets for all modules except the AHB bus matrix, cache

controller, fabric interface interrupt controller (FIIC), RTC, and SYSREG. These blocks will be reset at

power-on reset or system reset. The Reset Controller receives block enable bits and soft reset requests

(SOFT_RESET_CR bits) for various blocks within the MSS from SYSREG to control the block level reset

generation. The Reset Controller also generates four GPIO resets which will reset each bank of GPIO

signals, as described in the MSS GPIO Bank Resets Generator, page 659.

The following figure shows the block level resets from the Reset Controller along with the source of the

resets.

Figure 288 • Reset Controller With Only Block Level Resets

21.2.6.1 Cortex-M3 Processor Resets

The Reset Controller drives various reset signals to the Cortex-M3 processor as listed below:

1. M3_PORESET_M3_CLK_N

2. M3_PORESET_TCK_N

3. T_RESET_N

4. M3_SYS_RESET_N

5. M3_TRST_N

The source of the Cortex-M3 processor reset captured in the RESET_SOURCE_CR register (defined in

Table 648, page 669). The register captures the status of the resets so that once the Cortex-M3

processor comes out of reset, it can read this register and take further necessary action.

Cortex-M3 processor reset signal generation is explained in the following sections.

21.2.6.1.1 M3_PORESET_M3_CLK_N

This signal resets all logic within the Cortex-M3 processor except the debug logic.

M3_PORESET_M3_CLK_N is a synchronized signal of PO_RESET_N on M3_CLK. It asserts

asynchronously and negates synchronously to M3_CLK.

21.2.6.1.2 M3_PORESET_TCK_N

This is a reset signal to the Cortex-M3 processor. M3_PORESET_TCK_N is a synchronized signal of

PO_RESET_N on TCK (JTAG clock from the clock controller). It asserts asynchronously and negates

synchronously to TCK.

ZĞƐĞƚŽŶƚƌŽůůĞƌ

WĞƌŝƉŚĞƌĂůƐ

ůŽĐŬƌĞƐĞƚƐ

DZ

DZ

ͺ

Z

ͺ

KZ

ͺ

Z^d

ͺ

E

DZ

ͺ

W

ͺ

^

ͺ

Z^d

ͺ

E

&W'

ĨĂďƌŝĐ

'W/K

ͺ

Z^d

ͺ

E

D

ϯͺ

Z^d

ͺ

E

^z^Z'

tK'

ͺ

E>

D^^

ͺ

'W/K

ͺ

^z^Z^d

ͺ

^>

^K&dͺZ^dͺZ

ďŝƚƐ

ŽƌƚĞdžͲDϯ

WƌŽĐĞƐƐŽƌ

D

ϯͺ

^z^

ͺ

Z^d

ͺ

E

D

ϯͺ

dZ^d

ͺ

E

DZ

ͺ

W

ͺ

Z^d

ͺ

E

DZ

ͺ

y/

ͺ

Z^d

ͺ

E

tĂƚĐŚĚŽŐ

dŝŵĞƌ

tK'

ͺ

Z^d

ͺ

E

D^^

'W/K

D^^

ͺ

'W/K

ͺ

Z^d

ͺ

E

D^^

ͺ

'W/K

E<

Z^d^

Loading...

Loading...