System Register Block

UG0331 User Guide Revision 15.0 707

Note: Do not change these register fields dynamically for 005 and 010 devices, see System Registers Behavior

for M2S005/010 Devices, page 682.

22.3.38.1 Clock Ratio

22.3.39 MSS DDR Fabric Alignment Clock Controller Configuration

Register 2

[4:2] APB0_DIVISOR 0 Indicates the ratio between CLK_A and APB_0_CLK. The user

can write to this field dynamically during run time, even when

the source clock is active. The allowed values are described in

Ta b le 6 95 , page 707.

[1:0] DIVISOR_A 0 Indicates the ratio between CLK_SRC and CLK_A. Allowed

values:

00: 1:1

01: 2:1

10: 3:1

11: Reserved

Configure this field statically. Do not write to this field while the

source clock is active.

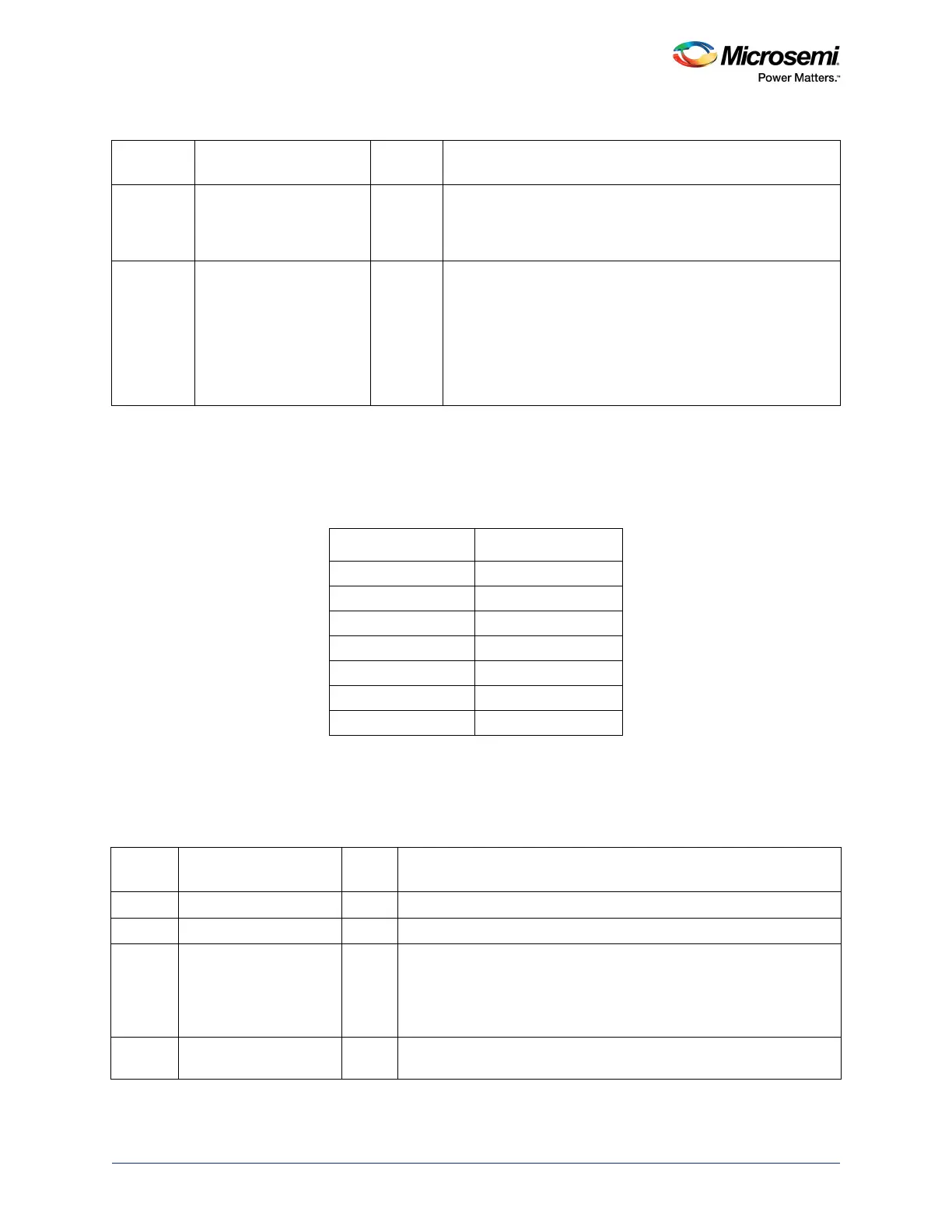

Table 695 • Clock Ratio

Bits Clock Ratio

000 1:1

001 2:1

010 4:1

100 8:1

101 16:1

110 32:1

Other values Reserved

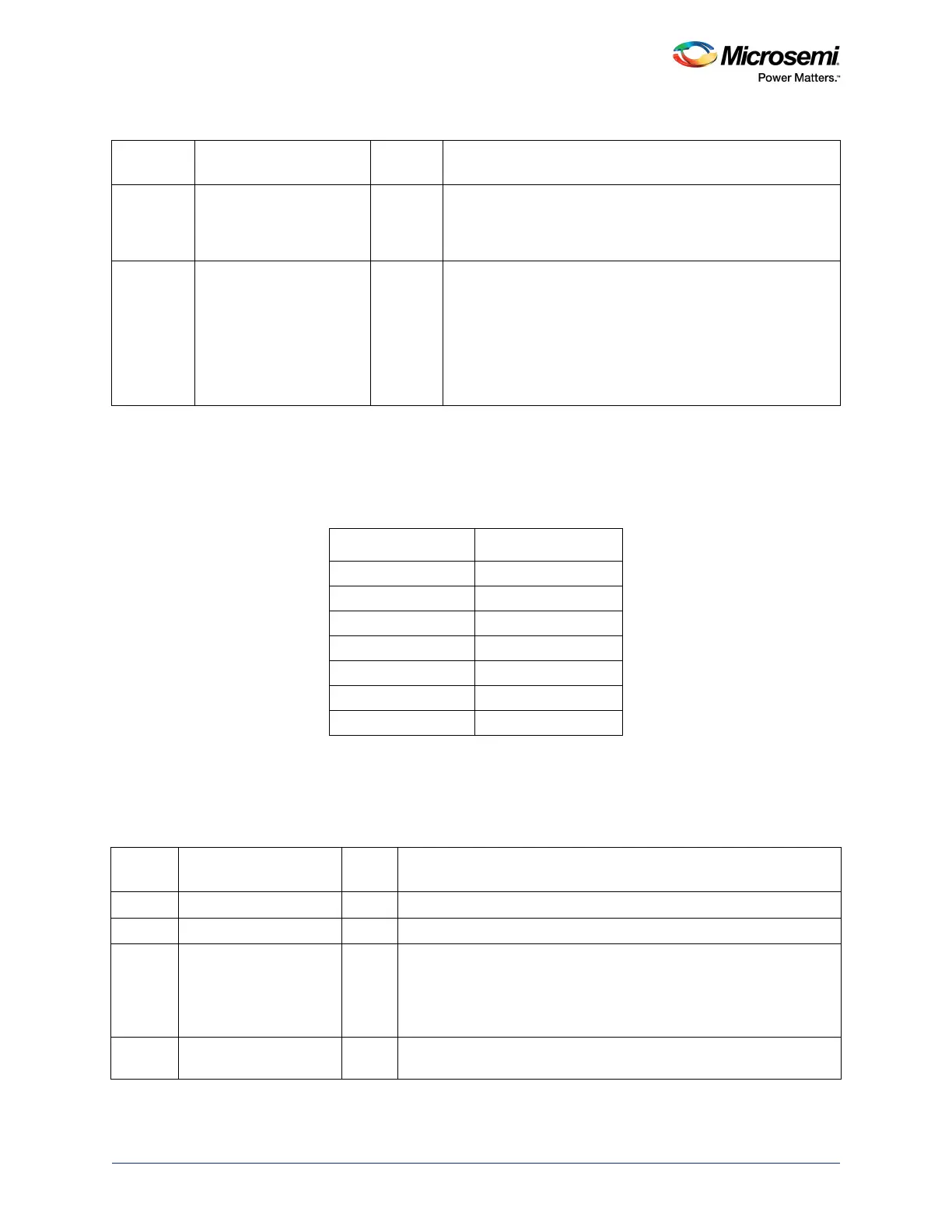

Table 696 • MSSDDR_FACC2_CR

Bit

Number Name

Reset

Value Description

[31:14] Reserved 0

13 MSS_XTAL_RTC_EN 0x1 Enable signal for auxiliary crystal oscillator (RTC crystal oscillator)

12 MSS_XTAL_EN 0x1 Enables the signal for the main crystal oscillator. If the main crystal

oscillator is selected as the MSS Flash*Freeze clock source, this bit

must be asserted at all times (even when not in Flash*Freeze mode).

1: Enable

0: Disable

11 MSS_CLK_ENVM_EN 0x1 Enables internal eNVM RC oscillator. Configure this field statically. Do

not write to this field while the source clock is active.

Table 694 • MSSDDR_FACC1_CR (continued)

Bit Number Name

Reset

Value Description

Loading...

Loading...