Cortex-M3 Processor (Reference Material)

UG0331 User Guide Revision 15.0 122

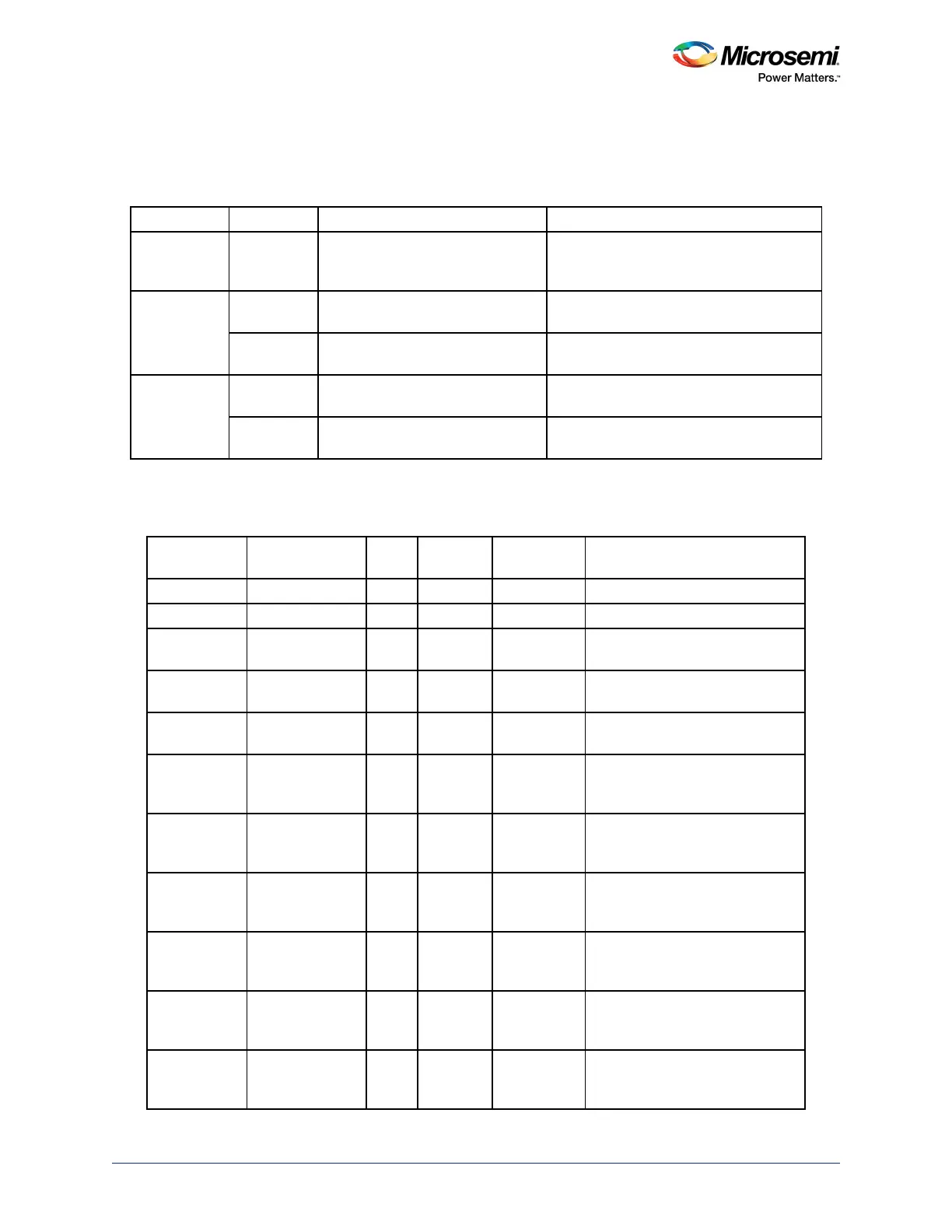

The following table shows the possible MPU region attributes. These include shareability and cache

behavior attributes that are not relevant to most microcontroller implementations. See MPU Configuration

for a Microcontroller, page 132 for guidelines for programming such an implementation.

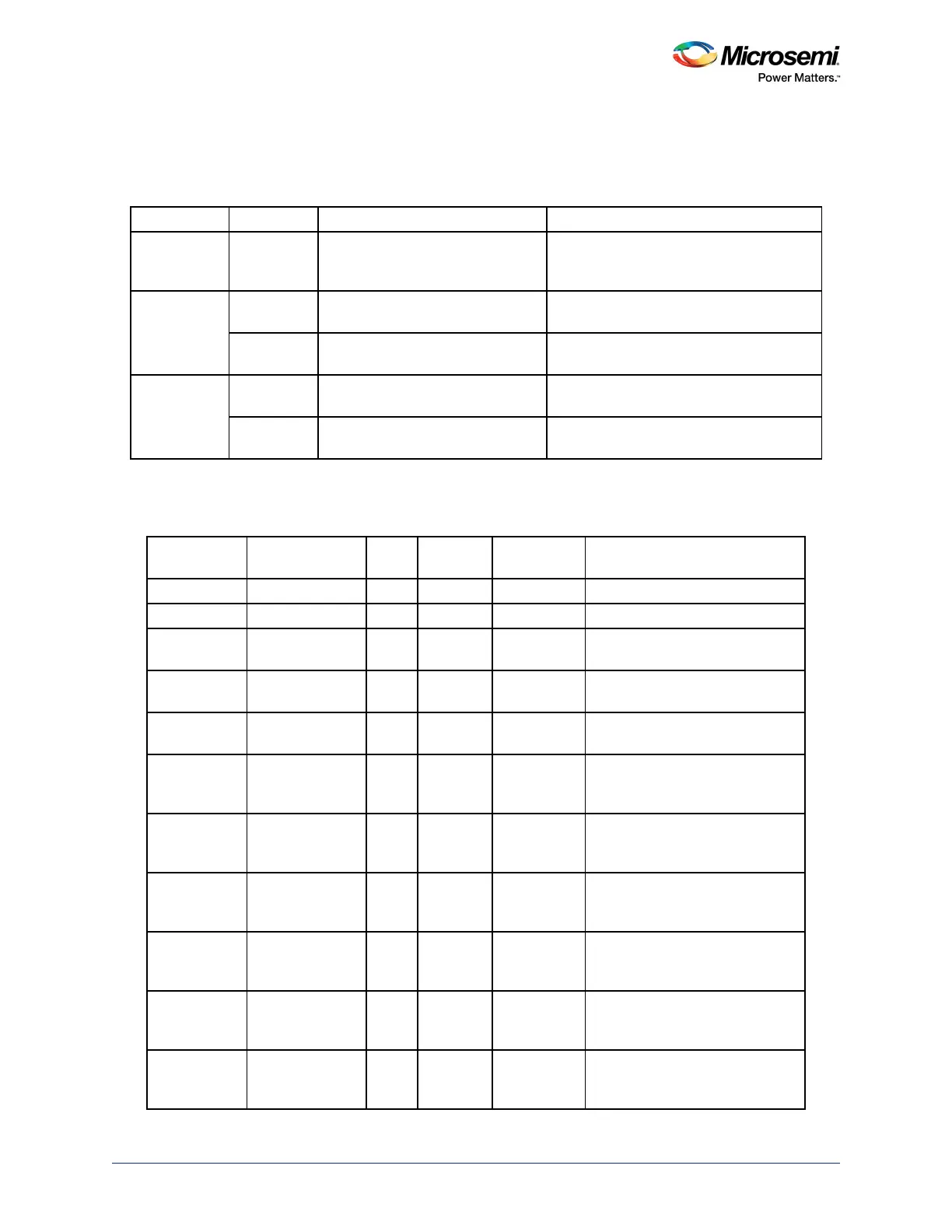

Use the MPU registers to define the MPU regions and their attributes. The MPU registers are:

Table 76 • Memory Attributes Summary

Memory Type Shareability Other Attributes Description

Strongly-

ordered

All accesses to Strongly-ordered memory

occur in program order. All Strongly-

ordered regions are assumed to be shared.

Device Shared Memory-mapped peripherals that several

processors share.

Non-shared Memory-mapped peripherals that only a

single processor uses.

Normal Shared Non-cacheable Write-through

Cacheable Write-back Cacheable

Normal memory that is shared between

several processors.

Non-shared Non-cacheable Write-through

Cacheable Write-back Cacheable

Normal memory that only a single

processor uses.

Table 77 • MPU Registers Summary

Address Name Type

Required

privilege

Reset

value See

0xE000ED90 MPU_TYPE RO Privileged 0x00000800 MPU Type Register, page 124

0xE000ED94 MPU_CTRL RW Privileged 0x00000000 MPU Control Register, page 124

0xE000ED98 MPU_RNR RW Privileged 0x00000000 MPU Region Number Register,

page 125

0xE000ED9C MPU_RBAR RW Privileged 0x00000000 MPU Region Base Address

Register, page 126

0xE000EDA0 MPU_RASR RW Privileged 0x00000000 MPU Region Attribute and Size

Register, page 127

0xE000EDA4 MPU_RBAR_A1 RW Privileged 0x00000000 Alias of MPU_RBAR, see MPU

Region Base Address Register,

page 126

0xE000EDA8 MPU_RASR_A1 RW Privileged 0x00000000 Alias of MPU_RASR, see MPU

Region Attribute and Size

Register, page 127

0xE000EDAC MPU_RBAR_A2 RW Privileged 0x00000000 Alias of MPU_RBAR, see MPU

Region Base Address Register,

page 126

0xE000EDB0 MPU_RASR_A2 RW Privileged 0x00000000 Alias of MPU_RASR, see MPU

Region Attribute and Size

Register, page 127

0xE000EDB4 MPU_RBAR_A3 RW Privileged 0x00000000 Alias of MPU_RBAR, see MPU

Region Base Address Register,

page 126

0xE000EDB8 MPU_RASR_A3 RW Privileged 0x00000000 Alias of MPU_RASR, see MPU

Region Attribute and Size

Register, page 127

Loading...

Loading...