Ethernet MAC

UG0331 User Guide Revision 15.0 402

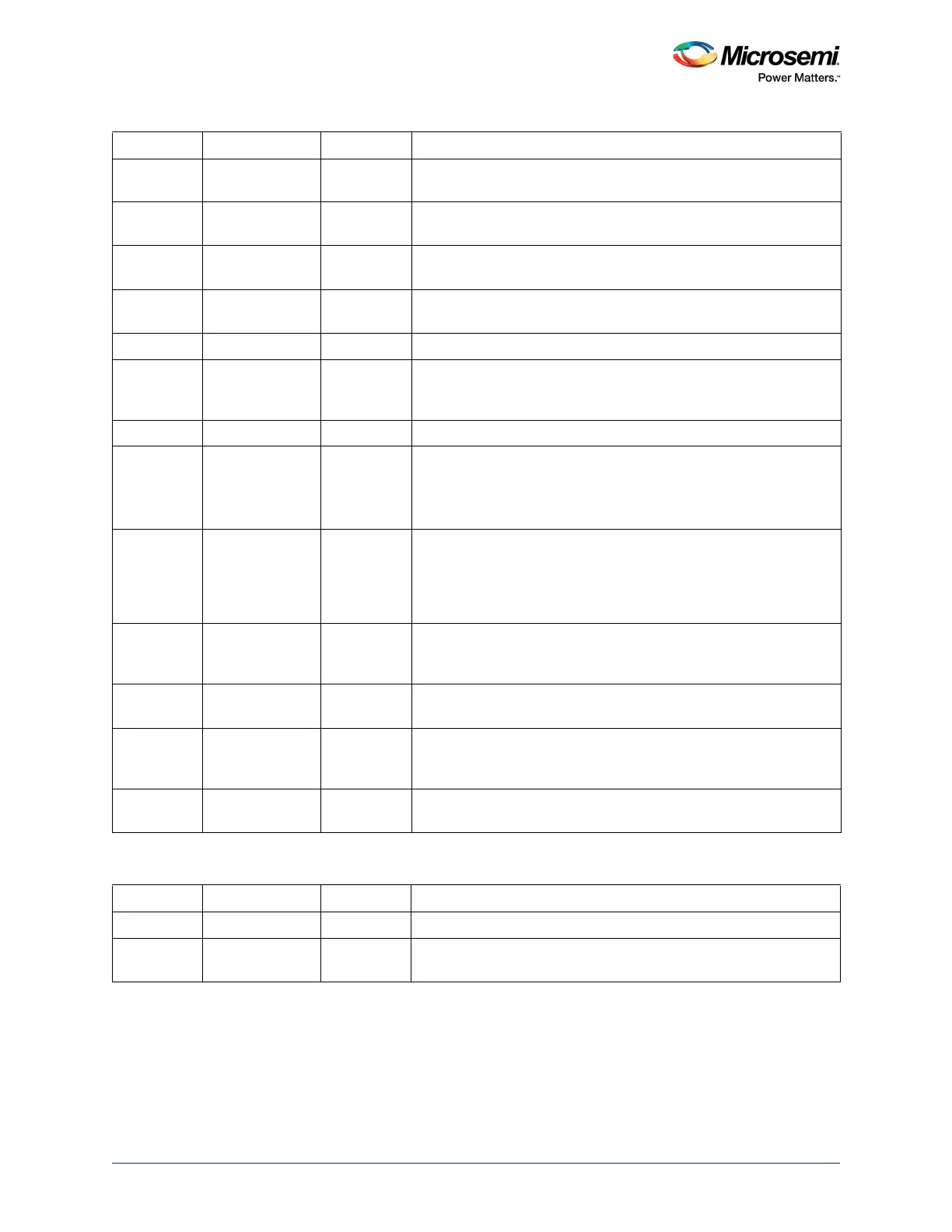

19 RESET RX MAC

CONTROL

0x0 Setting this bit puts the PERMC Receive MAC control in reset.

18 RESET TX MAC

CONTROL

0x0 Setting this bit puts the PETMC Transmit MAC control in reset.

17 RESET RX

FUNCTION

0x0 Setting this bit puts the PERFN receive function block in reset.

PERFN block performs the receive frame protocol.

16 RESET TX

FUNCTION

0x0 Setting this bit puts the PETFN transmit function block in reset.

PETFN block performs the frame transmission protocol.

[15:9] Reserved 0x0 Reserved

8 LOOP BACK 0x0 Setting this bit causes the PETFN MAC transmit outputs to be

looped back to the MAC receive inputs. Clearing this bit results in

normal operation.

[7:6] Reserved 0x0 Reserved

5 RECEIVE FLOW

CONTROL

ENABLE

0x0 Setting this bit causes the PERFN receive.

MAC Control to detect and act on PAUSE flow control frames.

Clearing this bit causes the receive MAC control to ignore PAUSE

flow control frames.

4 TRANSMIT

FLOW

CONTROL

ENABLE

0x0 Setting this bit allows the PETMC transmit.

MAC Control to send PAUSE flow control frames when requested by

the system.

Clearing this bit prevents the transmit MAC control from sending

flow control frames.

3 SYNCHRONIZE

D RECEIVE

ENABLE

0x0 This field is read only and indicates that the receive enable is

synchronized to the receive stream.

2 RECEIVE

ENABLE

0x0 Setting this bit allows the MAC to receive frames from the PHY.

Clearing this bit prevents the reception of the frames.

1 SYNCHRONIZE

D TRANSMIT

ENABLE

0x0 This field is read only and indicates that the transmit enable is

synchronized to the transmit stream.

0 TRANSMIT

ENABLE

0x0 Setting this bit allows the MAC to transmit frames from the system.

Clearing this bit prevents the transmission of the frames.

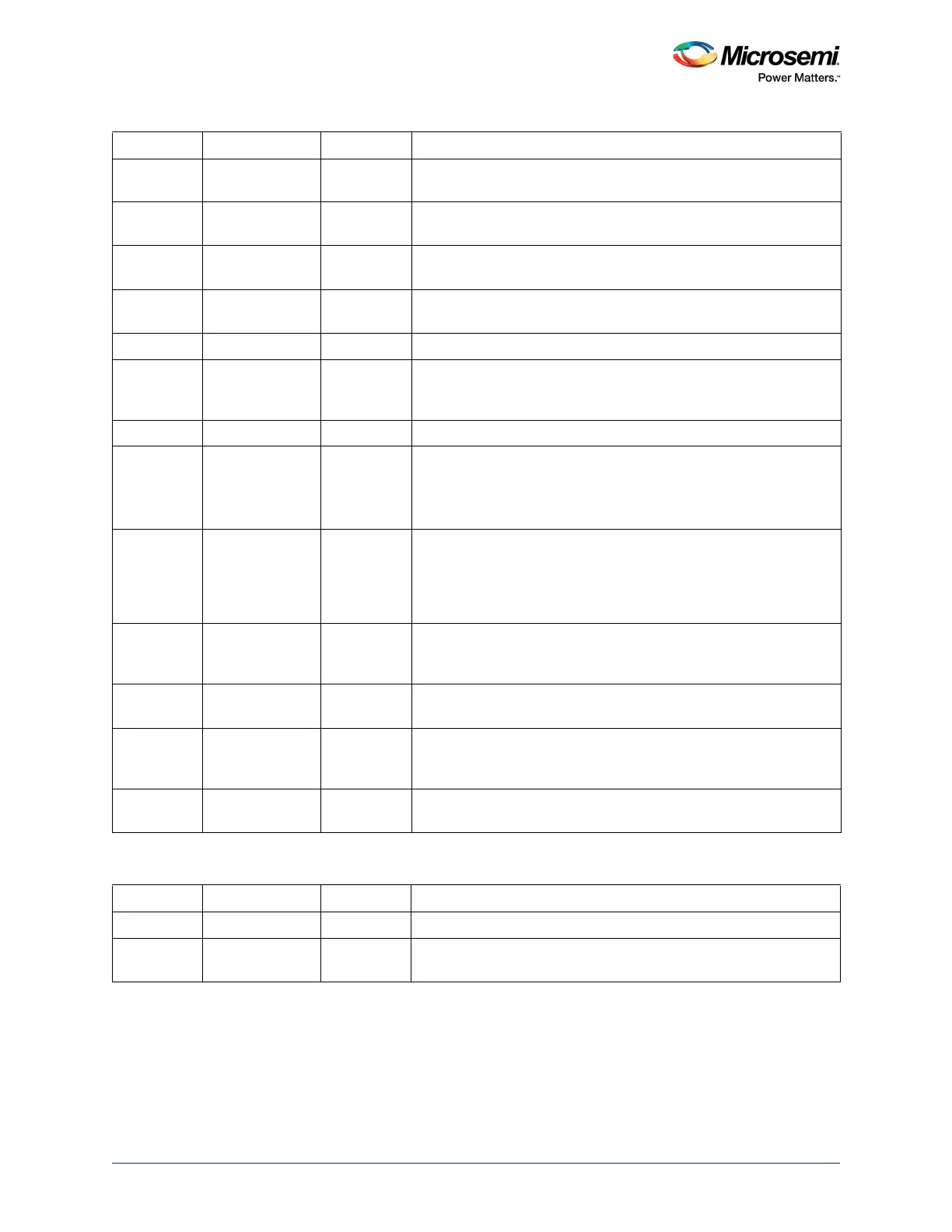

Table 348 • CFG2

Bit Number Name Reset Value Description

[31:16] Reserved 0x0 Reserved

[15:12] PREAMBLE

LENGTH

0x7 This field determines the length of the preamble field of the packet in

bytes. Default is ‘0x7’.

Table 347 • CFG1 (continued)

Bit Number Name Reset Value Description

Loading...

Loading...