System Register Block

UG0331 User Guide Revision 15.0 721

22.3.75 M3 Status Register

22.3.76 ETM Count Low Register

22.3.77 ETM Count High Register

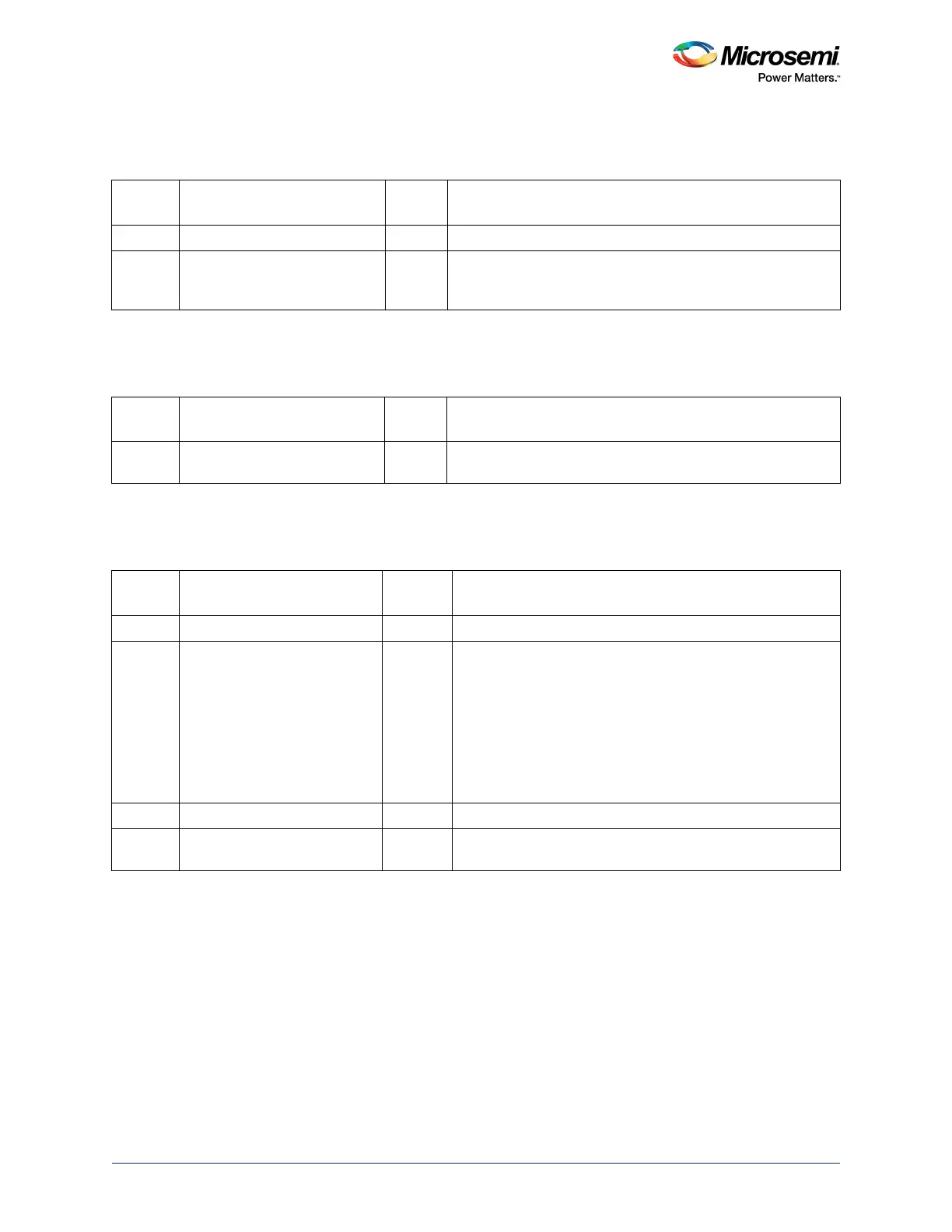

Table 732 • M3_SR

Bit

Number Name

Reset

Value Description

[31:8] Reserved 0

7:0 CURRPRI 0 Indicates which priority interrupt, or base boost, is being used

now. CURRPRI represents the pre-emption priority, and does

not indicate secondary priority.

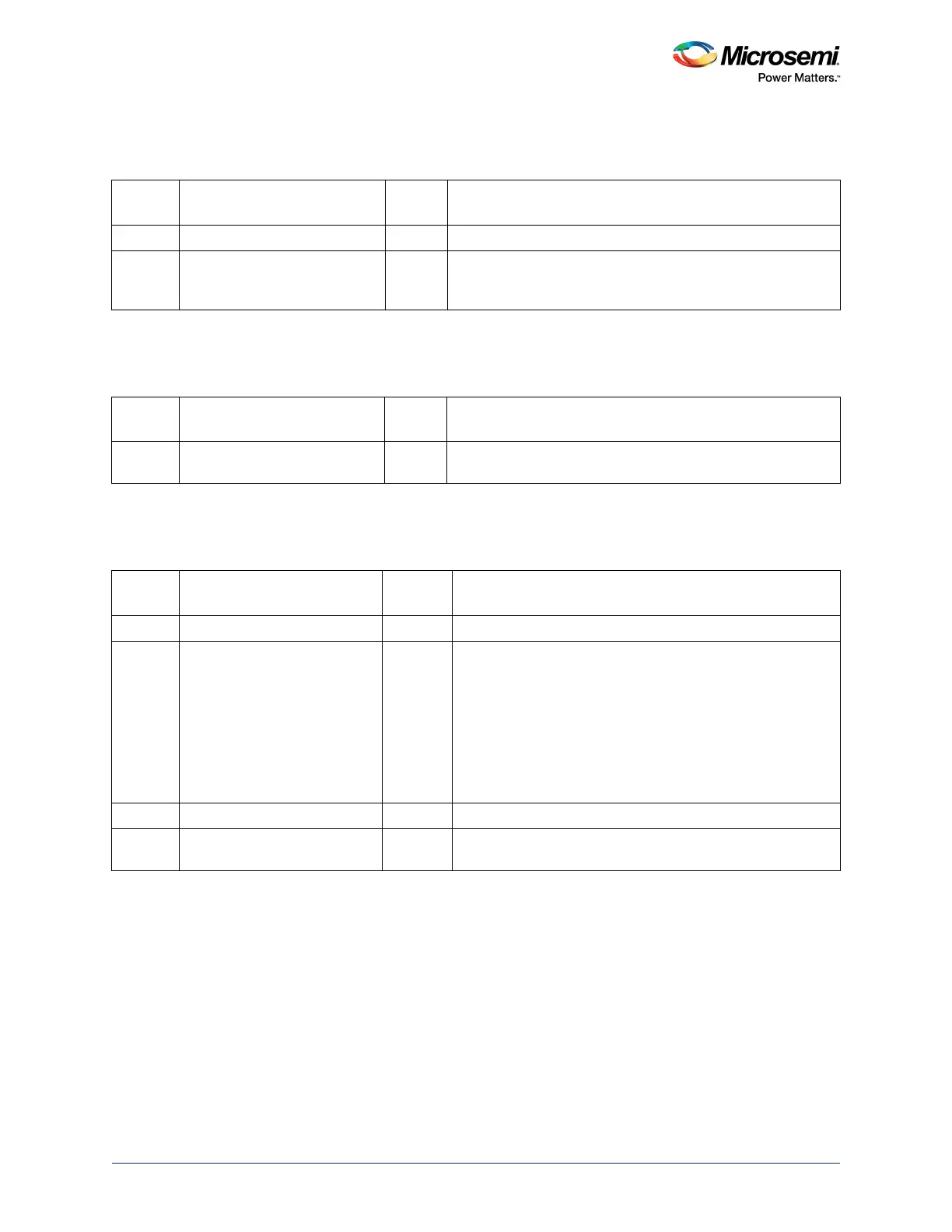

Table 733 • ETM_COUNT_LOW

Bit

Number Name

Reset

Value Description

[31:0] ETMCOUNT_31_0 0 Indicates the 32-bit lower bits of timestamp value (TSVALUEB)

from the Cortex-M3 processor.

Table 734 • ETM_COUNT_HIGH

Bit

Number Name

Reset

Value Description

[31:28] Reserved 0

[27:25] ETMINTSTAT 0 Indicates the interrupt status. The following bit definitions

mark the interrupt status of the current cycle:

000: No status

001: Interrupt entry

010: Interrupt exit

011: Interrupt return

100: Vector fetch and stack push

ETMINTSTAT entry or return is asserted in the first cycle of

the new interrupt context. Exit occurs without ETMIVALID.

[24:16] ETMINTNUM 0 Marks the interrupt number of current execution context.

[15:0] ETMCOUNT_47_32 0 Indicates the 47 to 32 of timestamp value (TSVALUEB) from

the Cortex-M3 processor.

Loading...

Loading...