System Register Block

UG0331 User Guide Revision 15.0 727

22.3.87 MSS DDR Clock Calibration Status

22.3.88 Watch Dog Load Register

22.3.89 Watch Dog MVRP Register

22.3.90 User Configuration Register 0

22.3.91 User Configuration Register 1

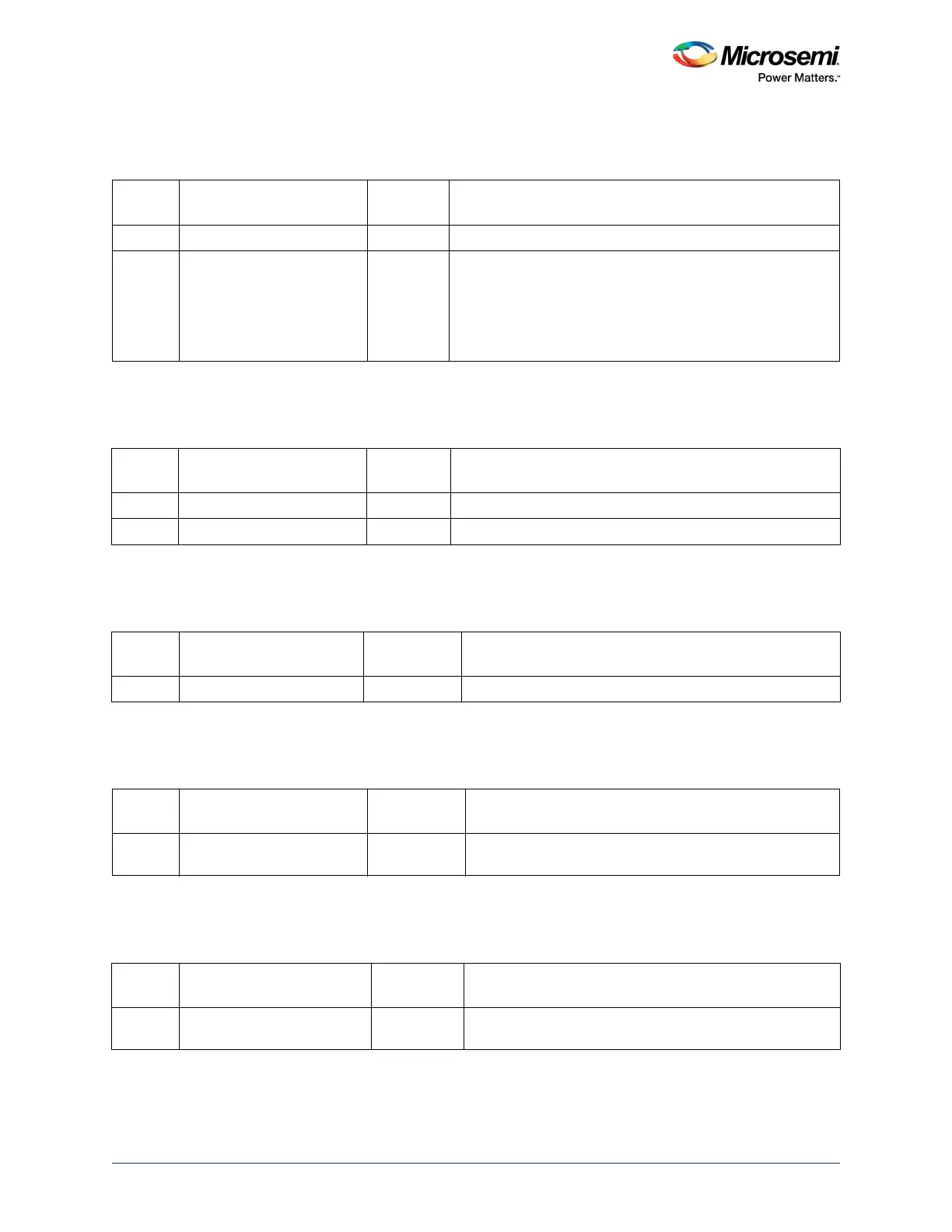

Table 744 • MSSDDR_CLK_CALIB_STATUS

Bit

Number Name

Reset

Value Description

[31:1] Reserved 0

0 FAB_CALIB_FAIL 0 0: The currently selected CCC delay values for the M3_CLK

and fabric Clock are such that the FPGA fabric clock

calibration circuit is running correctly.

1: The FPGA fabric clock calibration circuit is failing to operate

correctly. This indicates incorrectly configured delay values for

M3_CLK and/or fabric clock in the CCC.

Table 745 • WDOGLOAD

Bit

Number Name

Reset

Value Description

[31:26] Reserved 0

[25:0] WDOGLOAD 0x1800000 Contains upper 26 bits of the WDOGLOAD value register

Table 746 • WDOGMVRP

Bit

Number Name Reset Value Description

[31:0] WDOGMVRP 0xFFFFFFFF Contains the WDOGMVRP value

Table 747 • USERCONFIG0

Bit

Number Name Reset Value Description

[31:0] CONFIG_REG0 0 Stores the user configuration register 0 to be read by the

Cortex-M3 processor.

Table 748 • USERCONFIG1

Bit

Number Name Reset Value Description

[31:0] CONFIG_REG1 0 Stores the user configuration register 1 to be read by the

Cortex-M3 processor.

Loading...

Loading...