Cortex-M3 Processor (Reference Material)

UG0331 User Guide Revision 15.0 76

3.6.6 Multiply and Divide Instructions

The following table shows the multiply and divide instructions:

3.6.6.1 MUL, MLA, and MLS

Multiply, Multiply with Accumulate, and Multiply with Subtract, using 32-bit operands, and producing a

32-bit result.

3.6.6.1.1 Syntax

MUL{S}{cond} {Rd,} Rn, Rm ; Multiply

MLA{cond} Rd, Rn, Rm, Ra ; Multiply with accumulate

MLS{cond} Rd, Rn, Rm, Ra ; Multiply with subtract

where:

cond is an optional condition code, see Conditional Execution, page 55.

S is an optional suffix. If

S

is specified, the condition code flags are updated on the result of the operation,

see Conditional Execution, page 55.

Rd is the destination register. If

Rd

is omitted, the destination register is

Rn

.

Rn, Rm are registers holding the values to be multiplied.

Ra is a register holding the value to be added or subtracted from.

3.6.6.1.2 Operation

The

MUL

instruction multiplies the values from

Rn

and

Rm

, and places the least significant 32 bits of the

result in

Rd

.

The

MLA

instruction multiplies the values from

Rn

and

Rm

, adds the value from

Ra

, and places the least

significant 32 bits of the result in

Rd

.

The

MLS

instruction multiplies the values from

Rn

and

Rm

, subtracts the product from the value from

Ra

,

and places the least significant 32 bits of the result in

Rd

.

The results of these instructions do not depend on whether the operands are signed or unsigned.

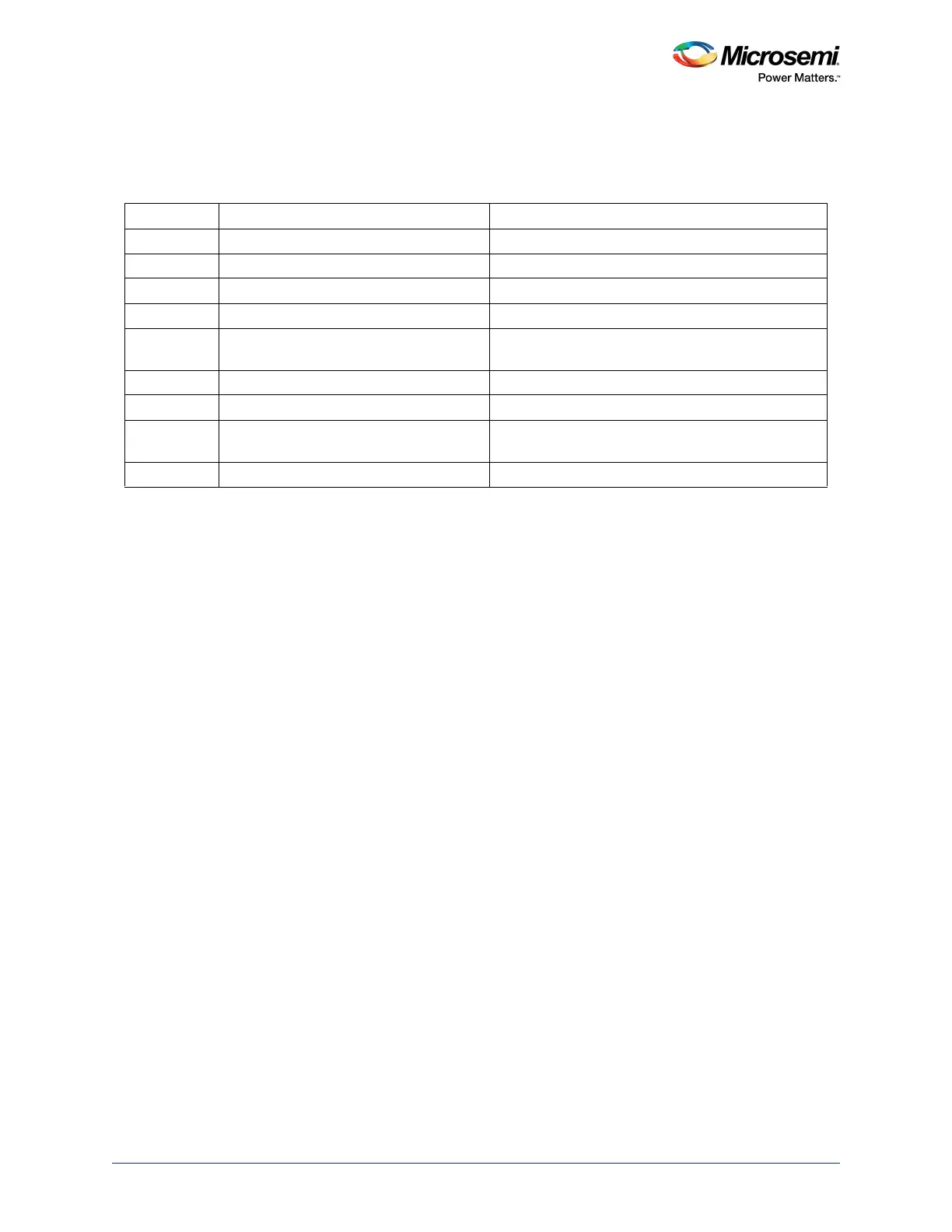

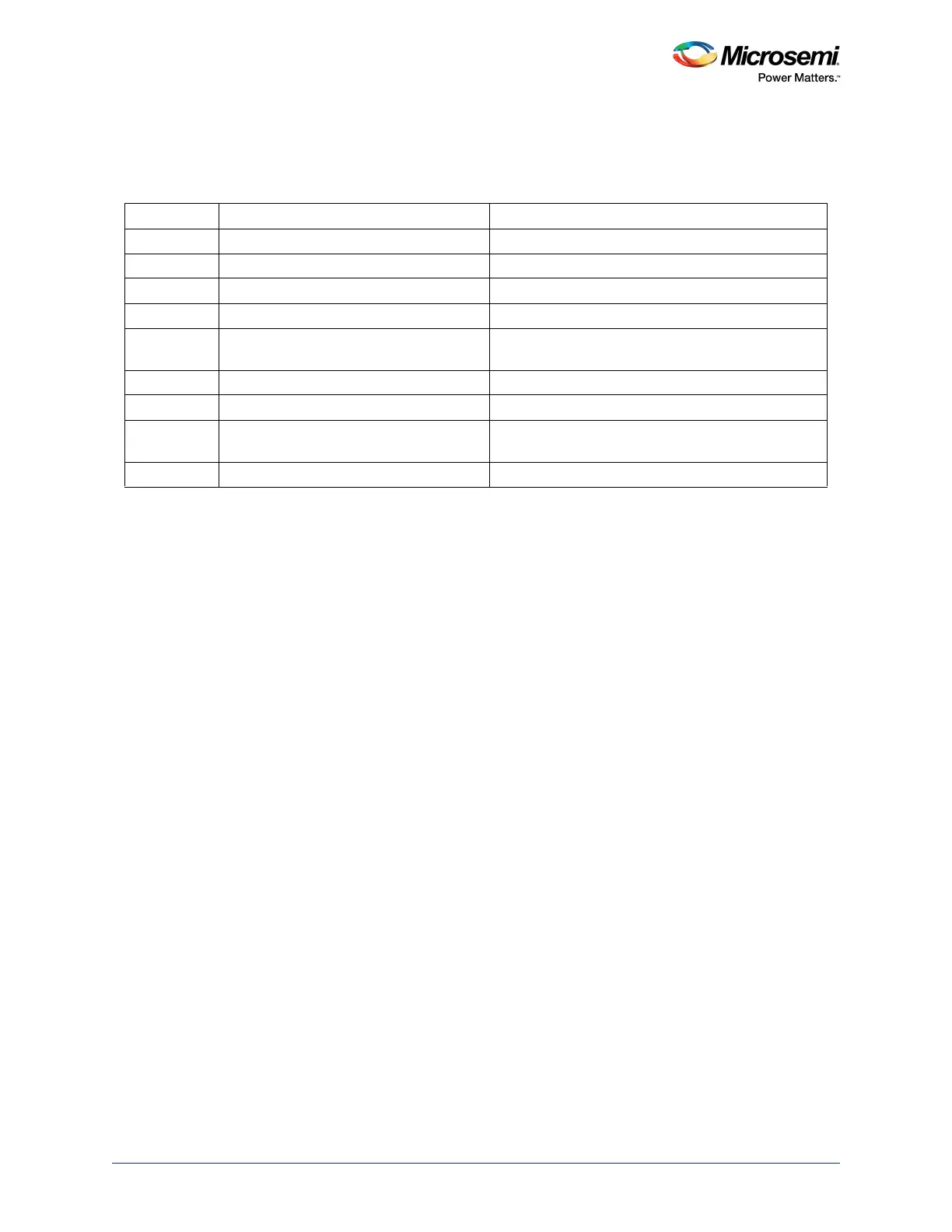

Table 34 • Multiply and Divide Instructions

Mnemonic Brief Description See

MLA Multiply with Accumulate, 32-bit result "MUL, MLA, and MLS" on page 71

MLS Multiply and Subtract, 32-bit result "MUL, MLA, and MLS" on page 71

MUL Multiply, 32-bit result "MUL, MLA, and MLS" on page 71

SDIV Signed Divide "SDIV and UDIV" on page 73

SMLAL Signed Multiply with Accumulate

(32x32+64), 64-bit result

"UMULL, UMLAL, SMULL, and SMLAL" on page 72

SMULL Signed Multiply (32x32), 64-bit result "UMULL, UMLAL, SMULL, and SMLAL" on page 72

UDIV Unsigned Divide "SDIV and UDIV" on page 73

UMLAL Unsigned Multiply with Accumulate

(32x32+64), 64-bit result

"UMULL, UMLAL, SMULL, and SMLAL" on page 72

UMULL Unsigned Multiply (32x32), 64-bit result "UMULL, UMLAL, SMULL, and SMLAL" on page 72

Loading...

Loading...