Inter-Integrated Circuit Peripherals

UG0331 User Guide Revision 15.0 556

Notes:

• SLA = Slave address

• SLV = Slave

• REC = Receiver

• TRX = Transmitter

• SLA+W = Master sends slave address then writes data to slave

• SLA+R = Master sends slave address then reads data from slave

15.4.2.4 Status Register – Slave-Transmitter Mode

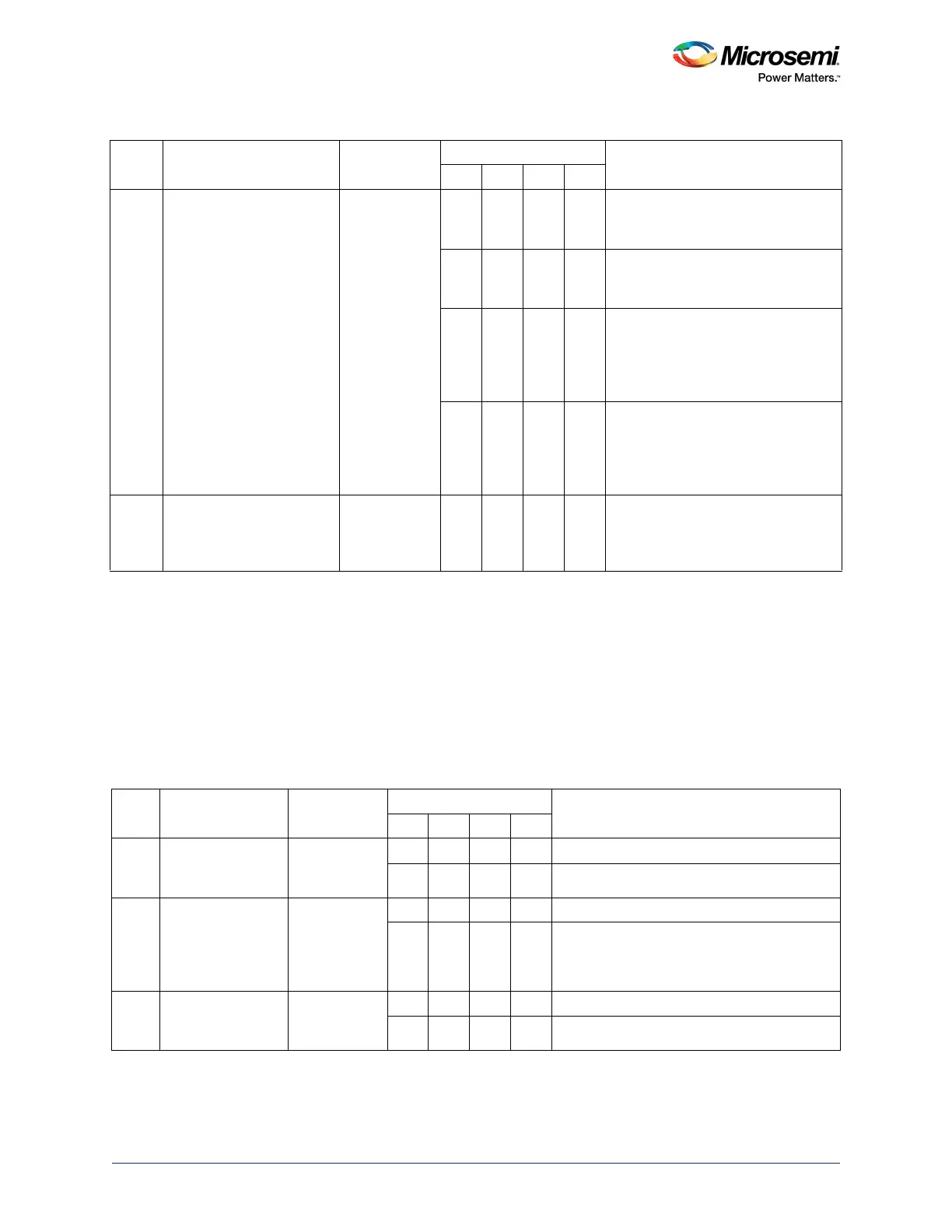

0xA0 A STOP condition or

repeated START condition

is received while addressed

as SLV/REC or SLV/TRX.

No action 0 0 0 0 Switched to not-addressed SLV

mode; no recognition of own SLA or

general call address.

0 0 0 1 Switched to not-addressed SLV

mode; own SLA or general call

address is recognized.

1 0 0 0 Switched to not-addressed SLV

mode; no recognition of own SLA or

general call address; START

condition is transmitted when the bus

gets free.

1 0 0 1 Switched to not-addressed SLV

mode; own SLA or general call

address is recognized; START

condition is transmitted when the bus

gets free.

0xD8 25 ms SCL low time is

reached; device must be

reset.

No action X 0 Slave must proceed to reset state by

clearing the interrupt within 10ms,

according to SMBus specification

v2.0.

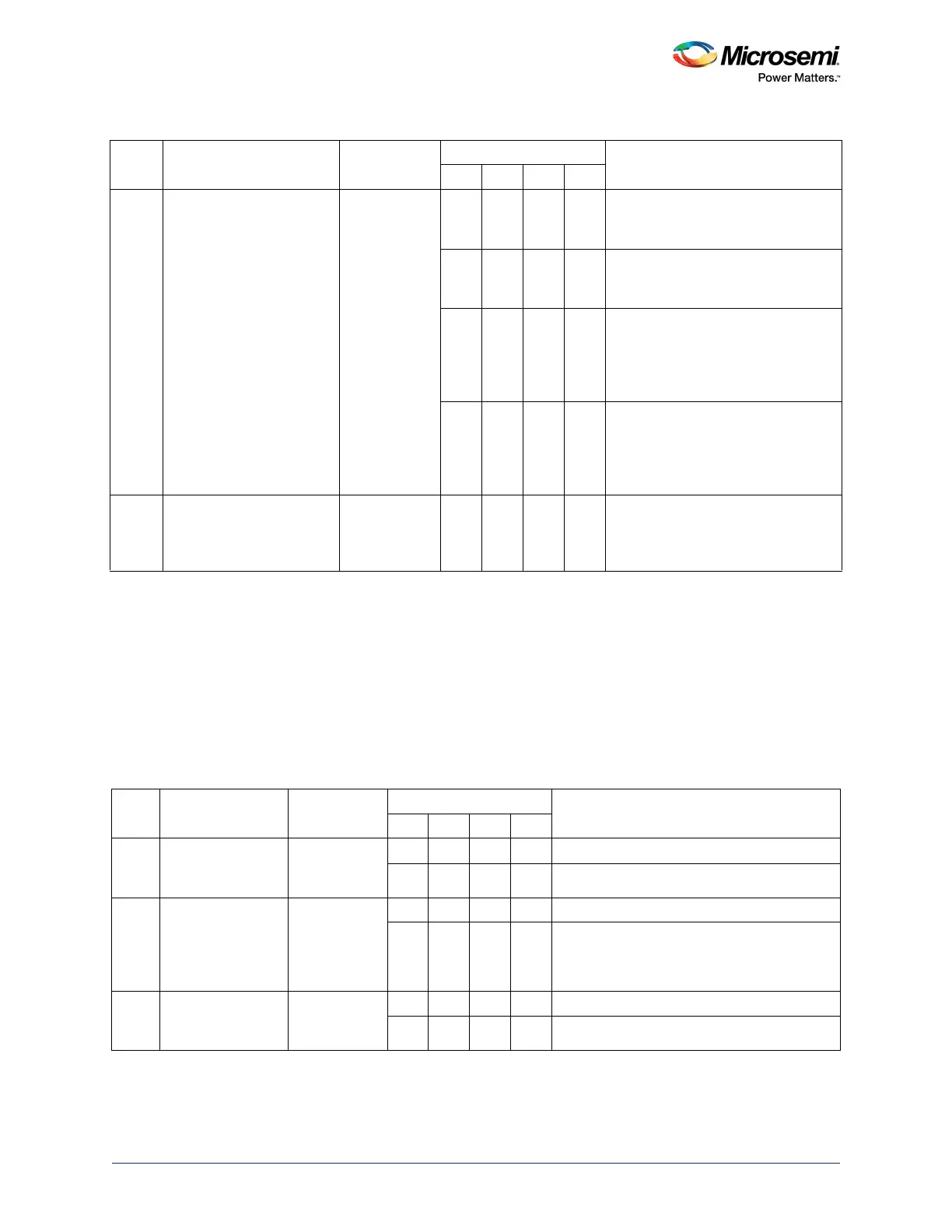

Table 527 • STATUS Register – Slave-Transmitter Mode

Status

Code Status

Data Register

Action

Control Register Bits

Next Action Taken by CoreSTA STO SI AA

0xA8 Own SLA+R is

received; ACK is

returned.

Load data byte 0 0 0 Last data byte is transmitted; ACK is received

0 0 1 Data byte is transmitted; ACK is received

0xB0 Arbitration lost in

SLA+R/W as

master; own

SLA+R is received;

ACK is returned.

Load data byte 0 0 0 Last data byte is transmitted; ACK is received

0 0 1 Data byte is transmitted; ACK is received

0xB8 Data byte is

transmitted; ACK is

received.

Load data byte 0 0 0 Last data byte is transmitted; ACK is received

0 0 1 Data byte is transmitted; ACK is received

Table 526 • STATUS Register – Slave-Receiver Mode (continued)

Status

Code Status

Data Register

Action

Control Register Bits

Next Action Taken by CoreSTA STO SI AA

Loading...

Loading...