System Register Block

UG0331 User Guide Revision 15.0 683

22.3.2 eSRAM Configuration Register

22.3.3 eSRAM Latency Configuration Register

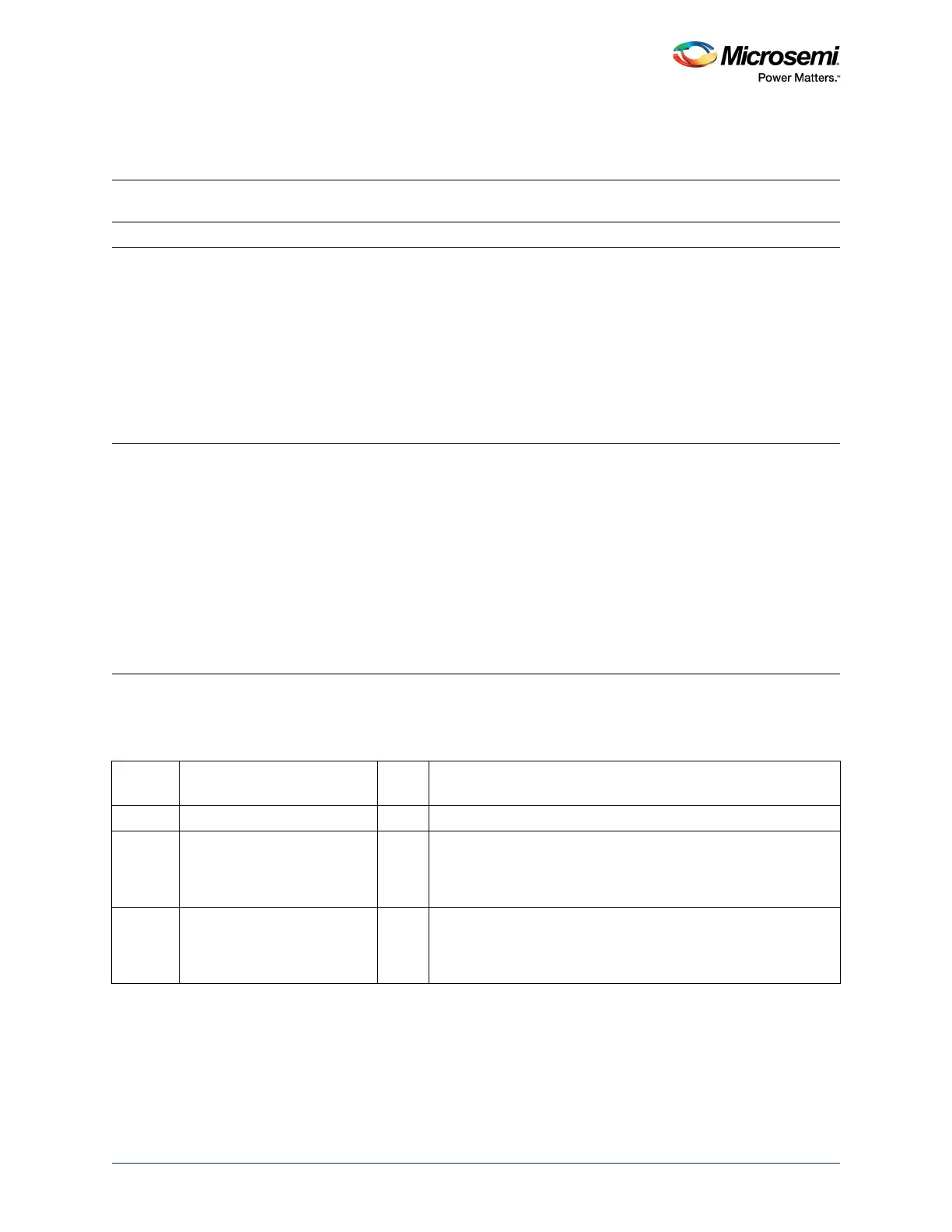

Table 652 • ESRAM_CR

Bit

Number Name

Reset

Value Description

[31:2] Reserved 0

1 SW_CC_ESRAM1FWREMAP 0 Defines the locations of eSRAM_0 and eSRAM_1 if eSRAM

remap is enabled (if SW_CC_ESRAMFWREMAP is asserted). If

SW_CC_ESRAMFWREMAP is 0, this bit has no meaning. If

SW_CC_ESRAMFWREMAP is 1, this bit has the following

definition:

0: eSRAM_0 is located at address 0x00000000 in the

ICODE/DCODE space of Cortex-M3 processor and eSRAM_1 is

located just above eSRAM_0 (adjacent to it).

1: eSRAM_1 is located at address 0x00000000 in

ICODE/DCODE space of Cortex-M3 processor and eSRAM_0 is

located just above eSRAM_1 (adjacent to it).

0 SW_CC_ESRAMFWREMAP 0 Indicates that eSRAM_0 and eSRAM_1 are remapped to

lCODE/DCODE space of the Cortex-M3 processor. If this bit is 1

and SW_CC_ESRAM1FWREMAP is 0, then eSRAM_0 is at

location 0x00000000 and eSRAM_1 is always remapped to be

just above eSRAM_0 (the two eSRAMs are adjacent in

ICODE/DCODE space). Both eSRAMs also remain visible in

SYSTEM space of the Cortex-M3 processor and remain visible at

this location to all other (non-Cortex-M3 processor) masters. The

bit definitions:

0: No eSRAM remap is enabled. This means that eNVM (or

MDDR) is present at location 0x00000000.

1: eSRAM_0 and eSRAM_1 are remapped to location

0x00000000 of Cortex-M3 processor ICODE/DCODE space.

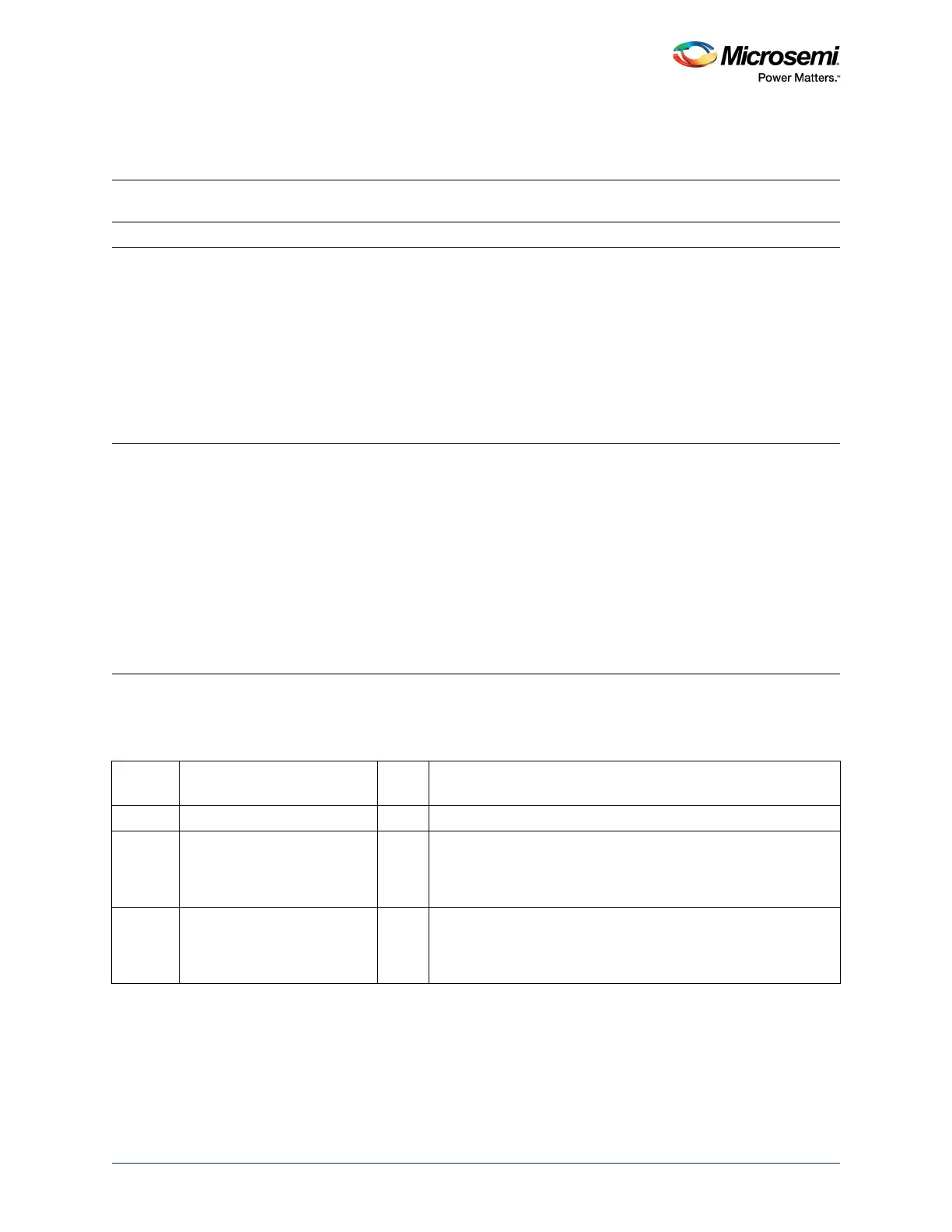

Table 653 • ESRAM_MAX_LAT

Bit

Number Name

Reset

Value Description

[31:6] Reserved 0

[5:3] SW_MAX_LAT_ESRAM1 0x1 Defines the maximum number of cycles the processor bus waits

for eSRAM1 when it is being accessed by a master with a WRR

priority scheme. The latency values are as given in Table 654,

page 684.

[2:0] SW_MAX_LAT_ESRAM0 0x1 Defines the maximum number of cycles the processor bus waits

for eSRAM0 when it is being accessed by a master with a WRR

priority scheme. It is configurable from 1 to 8 (8 by default). The

latency values are as given in Tabl e 654 , page 684.

Loading...

Loading...