Serial Peripheral Interface Controller

UG0331 User Guide Revision 15.0 534

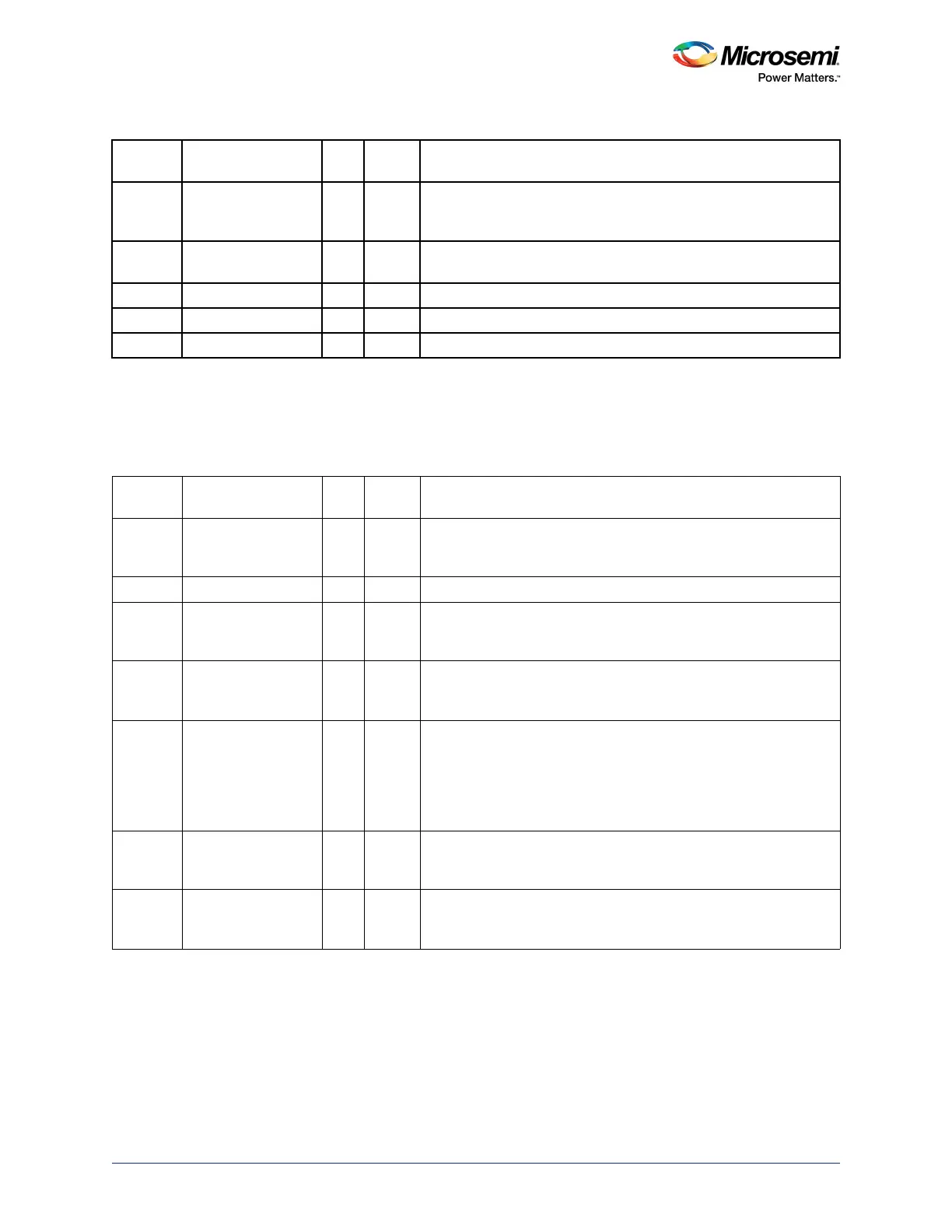

14.4.3.11 SPI Control2 Register

The following table describes the Control2 register details as the terminal frame counter, SPI slave

select, and auto status of SPI.

4 CMDINT R/W Indicates that the number of frames set by the CMDSIZE register

has been received as a single packet of frames (SPI_X_SS[x] held

active).

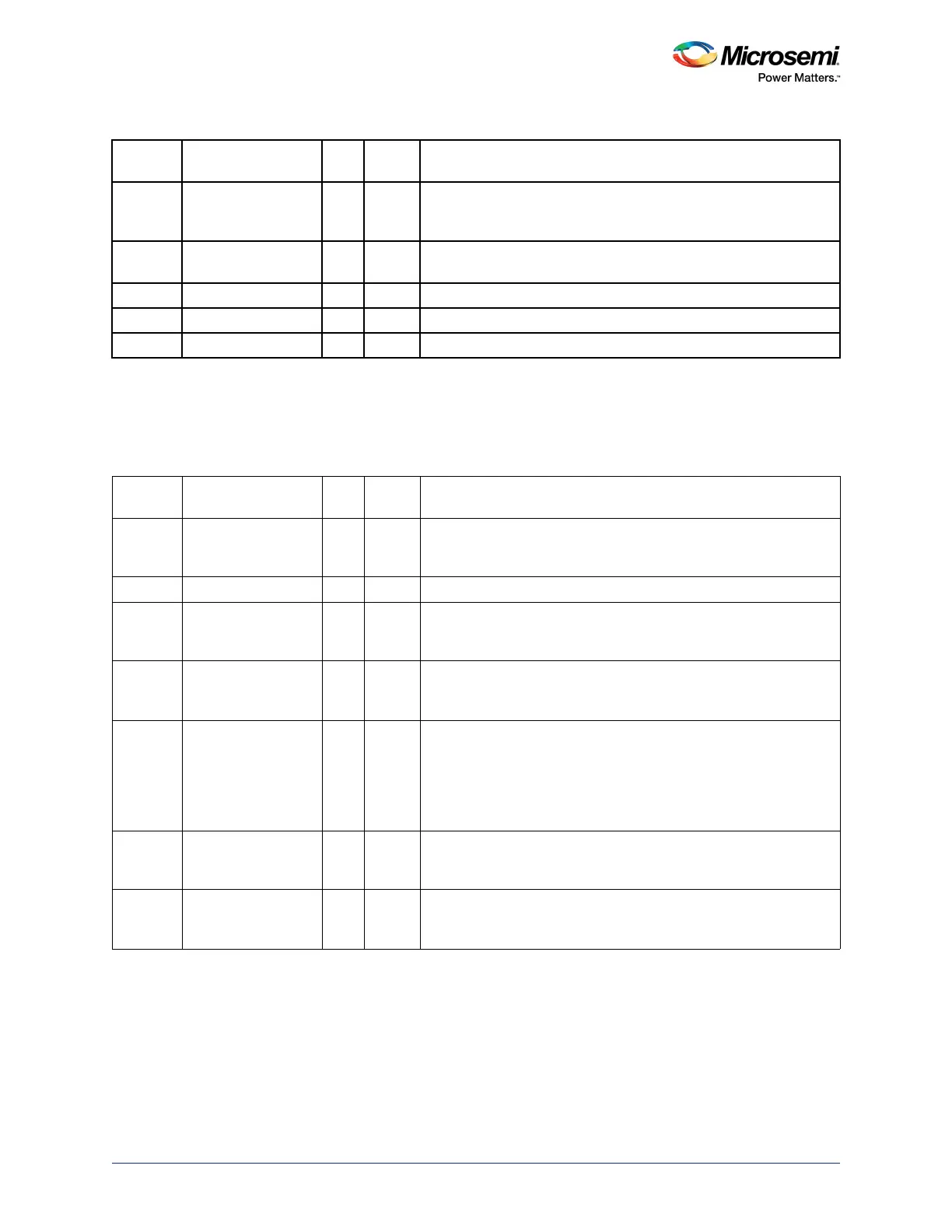

3 TXCHUNDR R 0 RAW interrupt status. Reading this returns raw interrupt status.

Raw status of transmit channel under-run

2 RXCHOVRF R 0 Raw status of receive channel overflow

1 RXRDY R 0 Receive data ready (data received in FIFO)

0 TXDONE R 0 Raw status of transmit done (data shifted out)

Table 511 • CONTROL2

Bit

Number Name R/W

Reset

Value Description

[31:6] Reserved R/W 0 Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should

be preserved across a read-modify-write operation.

5 INTEN_SSEND R/W Indicates that SPI_X_SS[x] has gone inactive.

4 INTEN_CMD R/W Indicates that the number of frames set by the CMDSIZE register

have been received as a single packet of frames (SPI_X_SS[x]

held active).

3 Reserved R/W 0 Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should

be preserved across a read-modify-write operation.

2 DISFRMCNT R/W 0 0: The internal frame counter is active. When the counter reaches

the programmed limit, it will pause the current SPI transfer inserting

idle cycles and generate the appropriate interrupts.

1: The internal frame counter is not active. The core transmits data

until the transmit FIFO empties. The FRAMECNT (CONTROL

register) should also be programmed to zero.

1 AUTOPOLL R/W 0 0: No effect

1: The first receive frame after SPI_X_SS[0] is active. It is

discarded (not written to the FIFO) and supports the POLL function.

0 AUTOSTATUS R/W 0 0: No effect

1: The first transmitted frame (slave mode) contains the hardware

status, not data from the transmit FIFO.

Table 510 • RIS

Bit

Number Name R/W

Reset

Value Description

Loading...

Loading...