AHB Bus Matrix

UG0331 User Guide Revision 15.0 234

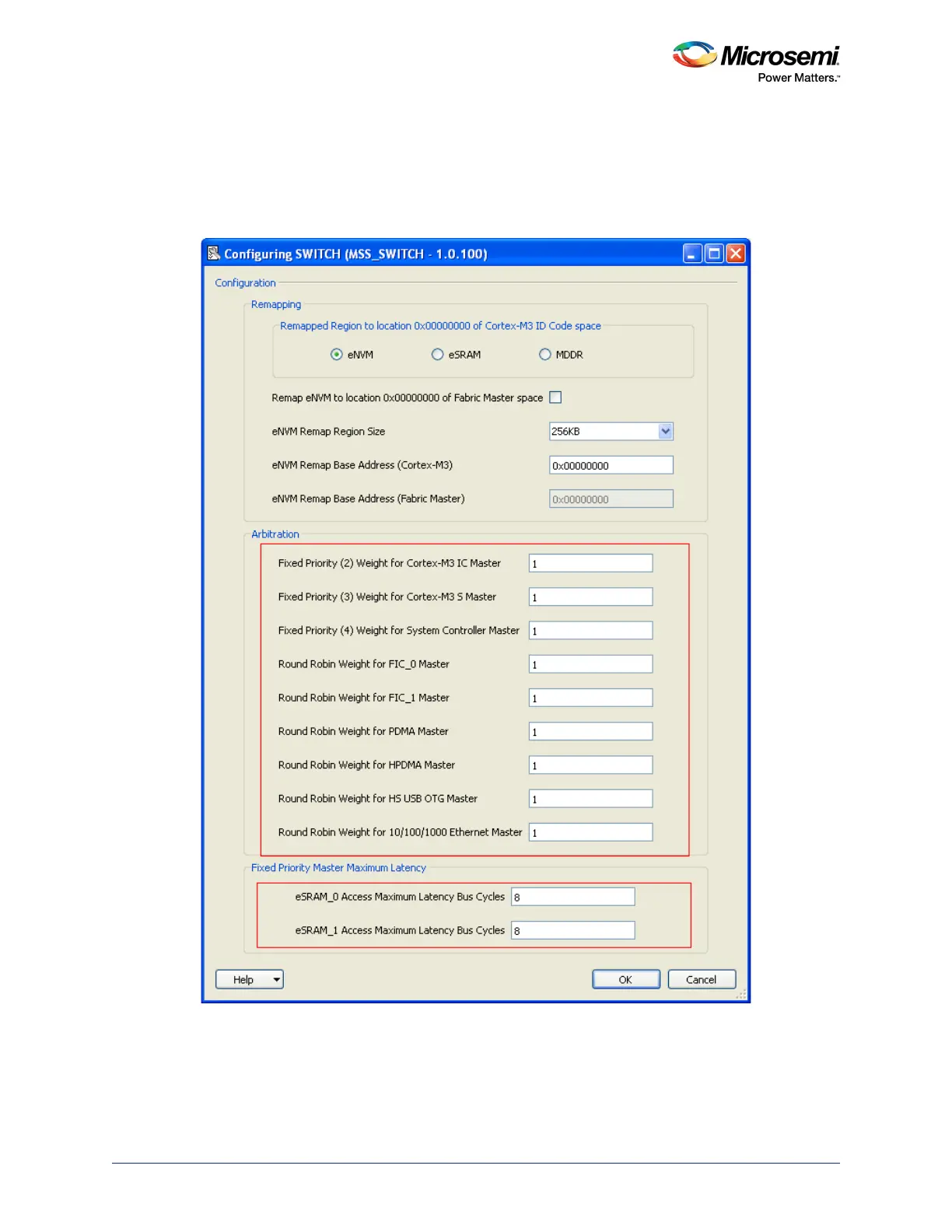

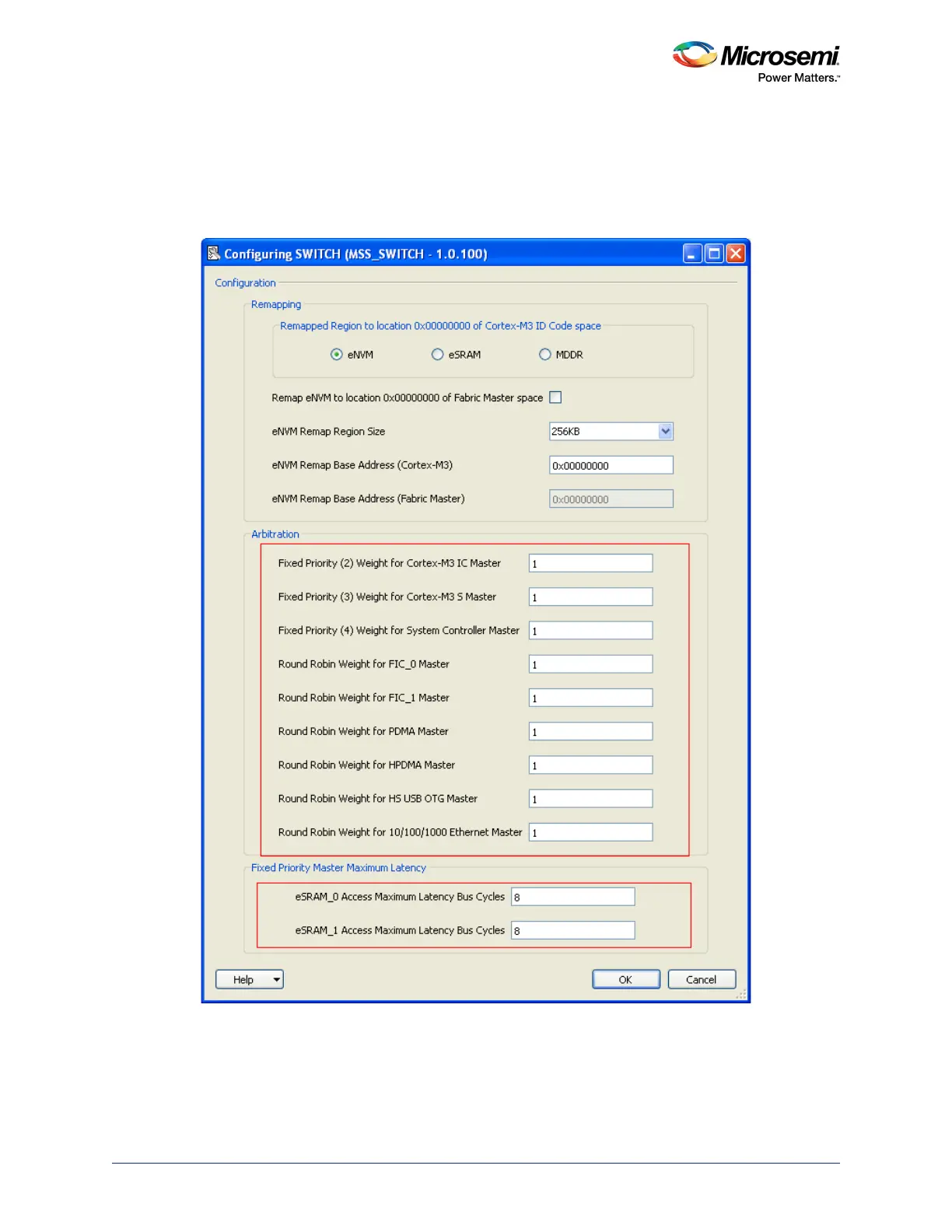

2. Click on AHB Bus Matrix to configure it. The AHB Bus Matrix configuration window is shown in the

following figure.

• The AHB bus matrix provides support to remap eNVM, eSRAM and DDR memory regions to

location 0x000000000 of the Cortex-M3 ID code space. It also provides an option to remap

eNVM for a Soft Processor eNVM Remap.To enable remapping for eNVM, eSRAM and DDR

select appropriate option from remapping section of AHB Bus Matrix configurator.

Figure 119 • AHB Bus Matrix Configuration Window

• Enter the weight values for the masters in arbitration section, to configure the programmable

weight registers MASTER_WEIGHT0_CR and MASTER_WEIGHT1_CR. These are located in

the SYSREG block with the required weight values. The weight values range is from 1 to 32.

• Enter the maximum latency values for the fixed priority masters to configure

ESRAM_MAX_LAT registers that are located in the SYSREG block.

This decides the peak wait time for a fixed priority master arbitrating for eSRAM access while

Loading...

Loading...