Ethernet MAC

UG0331 User Guide Revision 15.0 412

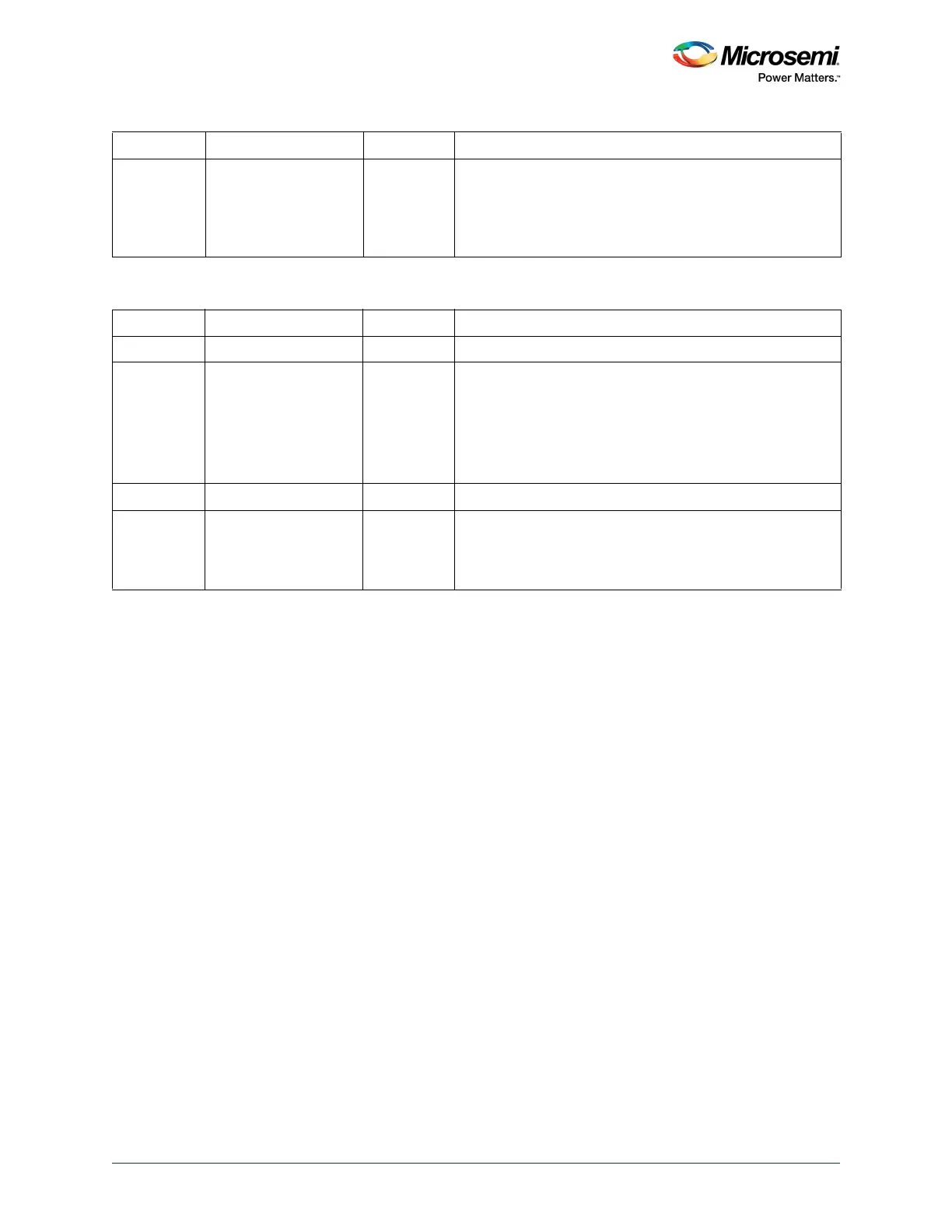

[15:13] Reserved 0x0 Reserved

[12:0] cfglwm 0x1FFF This bit represents the minimum number of 4 byte words that

are simultaneously stored in the receive RAM before transmit

flow control enables and pause value facilitates an XON

pause control frame in response to a previously transmitted

XOFF pause control frame.

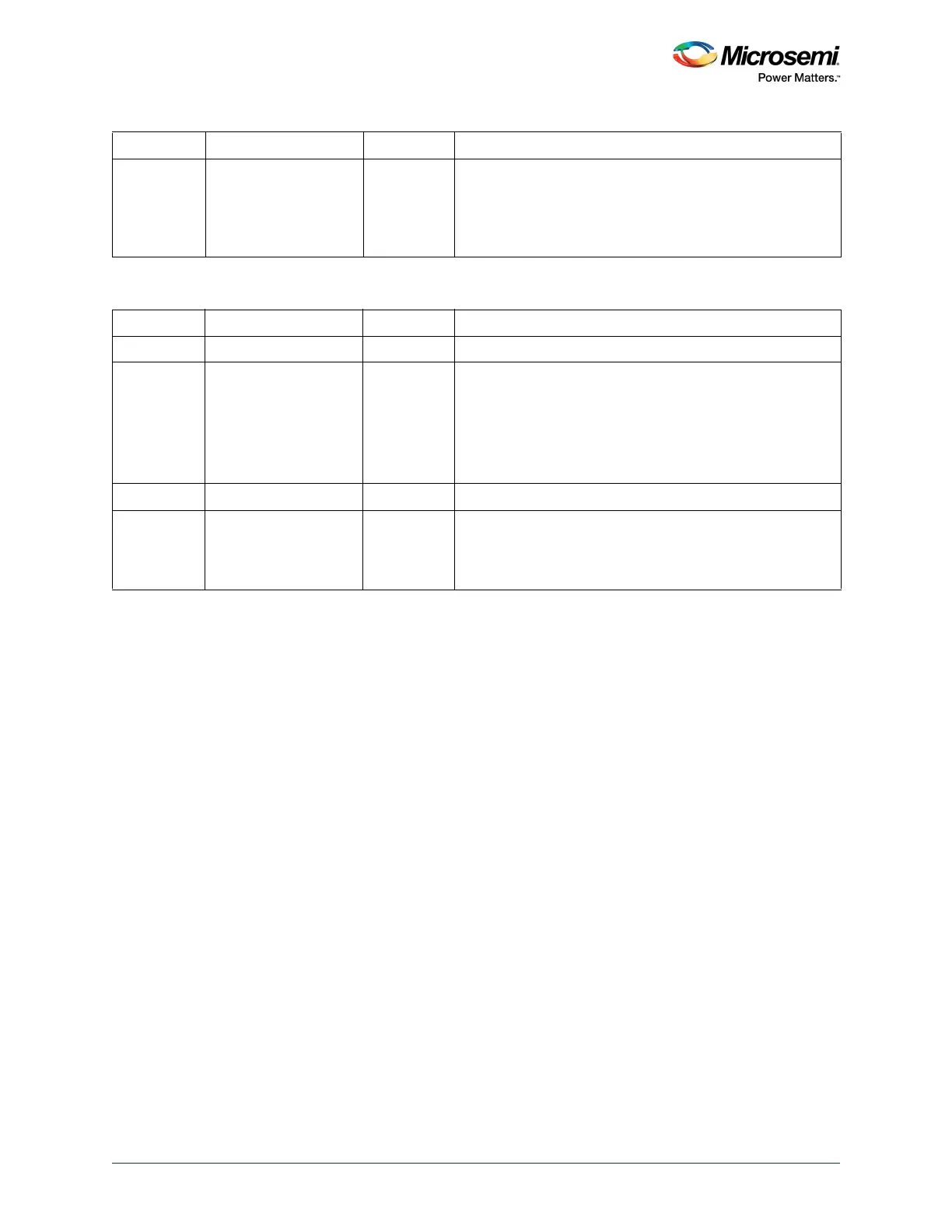

Table 366 • FIFO_CFG3

Bit Number Name Reset Value Description

[31:28] Reserved 0x0 Reserved

[27:16] cfghwmft 0xFFF This hex value represents the maximum number of 4 byte

locations, which are simultaneously stored in the transmit

RAM before the fthwm is asserted.

The fthwm is asserted whenever the amount of four byte

locations, used in the transmit FIFO data RAM, exceeds the

value programmed in the cfghwmft host register.

[15:12] Reserved 0x0 Reserved

[11:0] cfgftth 0xFFF This bit represents the minimum number of 4 byte locations

which are simultaneously stored in the transmit RAM, relative

to the beginning of the frame being input, before transmit

packet start of frame is asserted.

Table 365 • FIFO_CFG2 (continued)

Loading...

Loading...