Inter-Integrated Circuit Peripherals

UG0331 User Guide Revision 15.0 554

Notes:

• SLA = Slave address

• SLV = Slave

• REC = Receiver

• TRX = Transmitter

• SLA+W = Master sends slave address then writes data to slave

• SLA+R = Master sends slave address then reads data from slave

15.4.2.3 Status Register: Slave-Receiver Mode

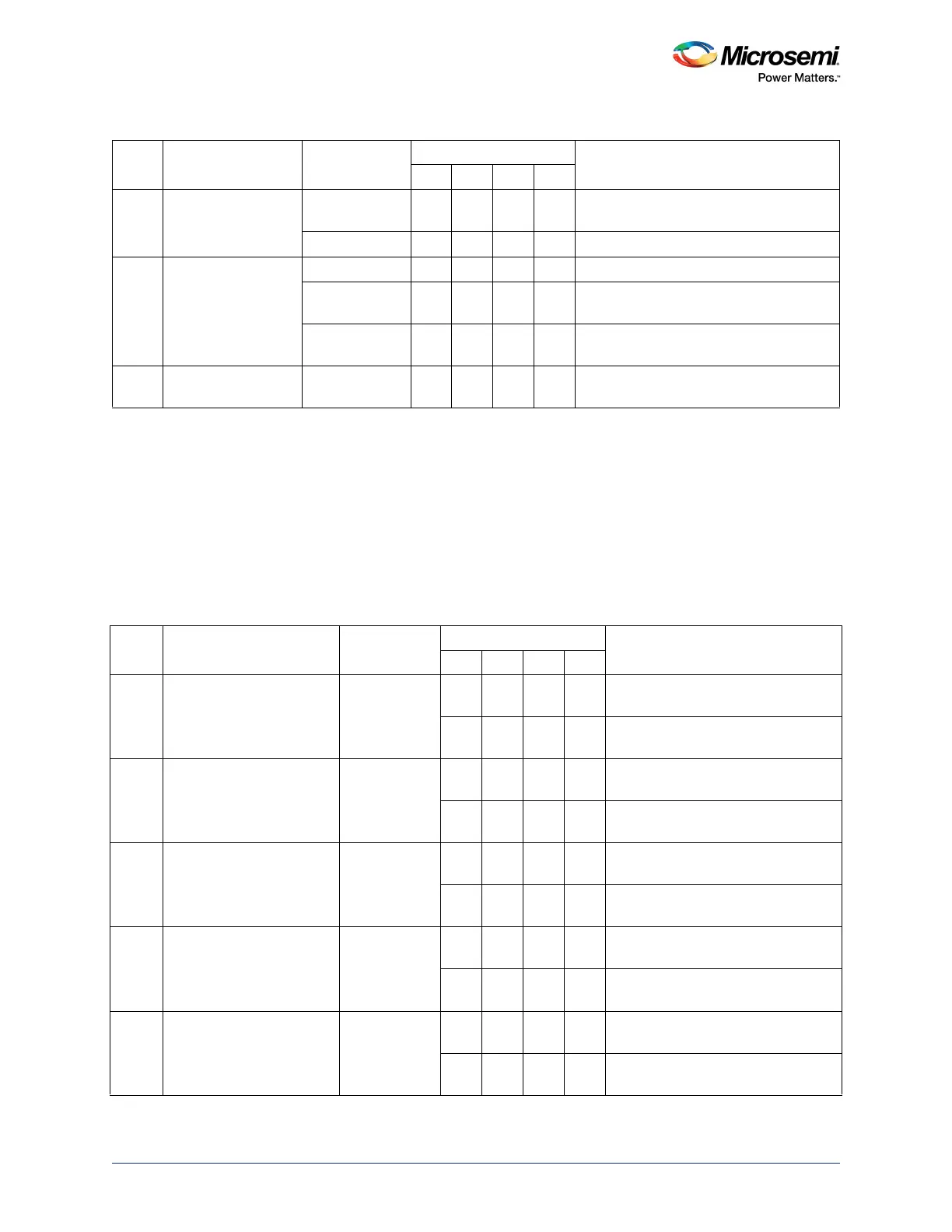

0x50 Data byte has been

received; ACK is

returned.

Read data byte 0 0 0 0 Data byte is received; not ACK(NACK) is

returned.

Read data byte 0 0 0 1 Data byte is received; ACK is returned

0x58 Data byte is received;

not ACK (NACK) is

returned.

Read data byte 1 0 0 Repeated START condition is transmitted

Read data byte 0 1 0 STOP condition is transmitted; STO flag

is reset.

Read data byte 1 1 0 STOP condition followed by a START

condition is transmitted; STO flag is reset.

0xD0 SMBus master reset

is activated.

No action 0 Wait 35 ms for interrupt to set, clear

interrupt and proceed to F8H state.

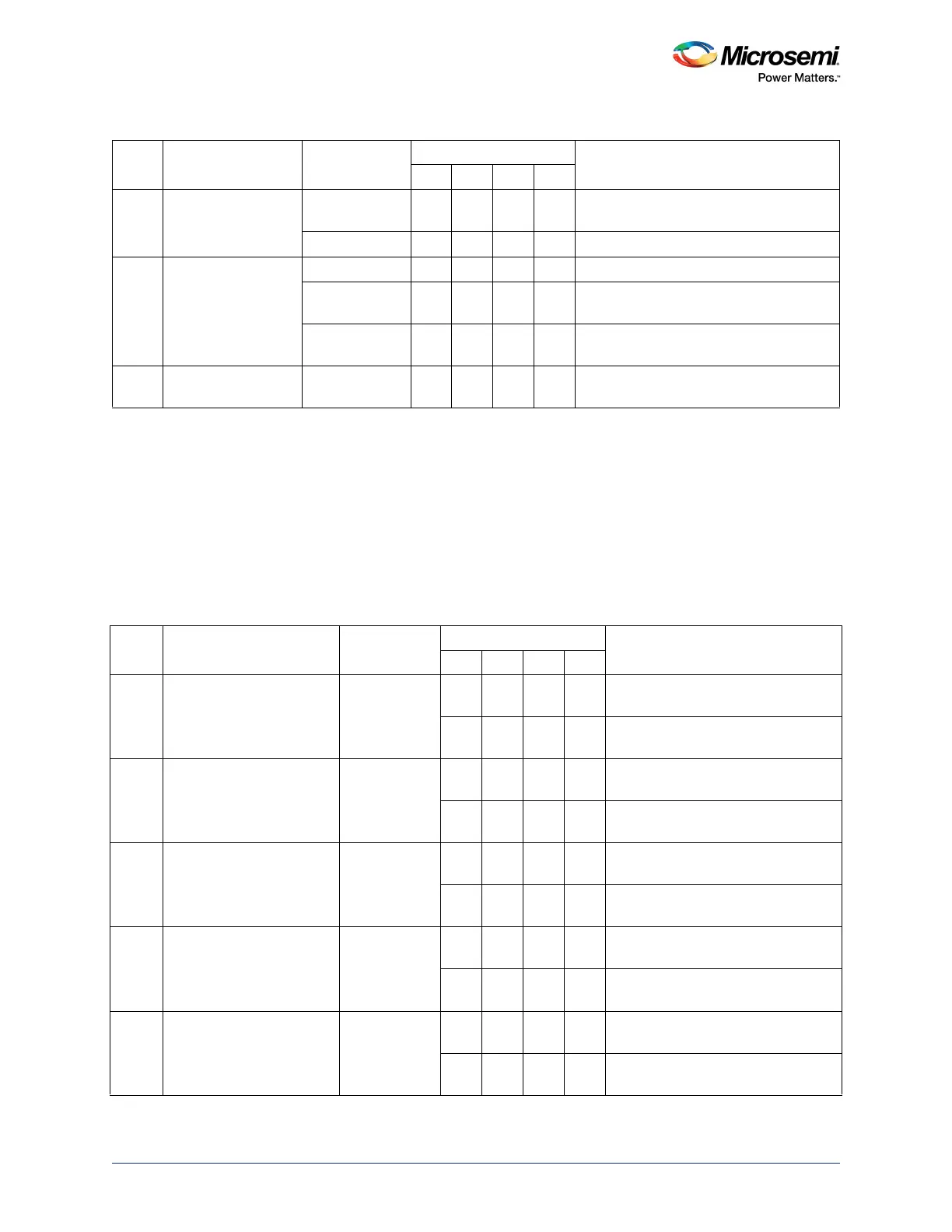

Table 526 • STATUS Register – Slave-Receiver Mode

Status

Code Status

Data Register

Action

Control Register Bits

Next Action Taken by CoreSTA STO SI AA

0x60 Own SLA+W is received;

ACK is returned.

No action 0 0 0 Data byte is received and not ACK

(NACK) is returned.

0 0 1 Data byte is received and ACK is

returned.

0x68 Arbitration lost in SLA+R/W

as master; own SLA+W is

received, ACK returned.

No action 0 0 0 Data byte is received and not ACK

(NACK) is returned.

0 0 1 Data byte is received and ACK is

returned.

0x70 General call address (00H)

is received; ACK is

returned.

No action 0 0 0 Data byte is received and not ACK

(NACK) is returned.

0 0 1 Data byte is received and ACK is

returned.

0x78 Arbitration lost in SLA+R/W

as master; general call

address is received, ACK

returned.

No action 0 0 0 Data byte is received and not ACK

(NACK) is returned.

0 0 1 Data byte is received and ACK is

returned.

0x80 Previously addressed with

own SLV address; DATA is

received; ACK returned.

Read data byte 0 0 0 Data byte is received and not ACK

(NACK) is returned.

0 0 1 Data byte is received and ACK is

returned.

Table 525 • STATUS Register – Master-Receiver Mode (continued)

Status

Code Status

Data Register

Action

Control Register Bits

Next Action Taken by CoreSTA STO SI AA

Loading...

Loading...