Cache Controller

UG0331 User Guide Revision 15.0 141

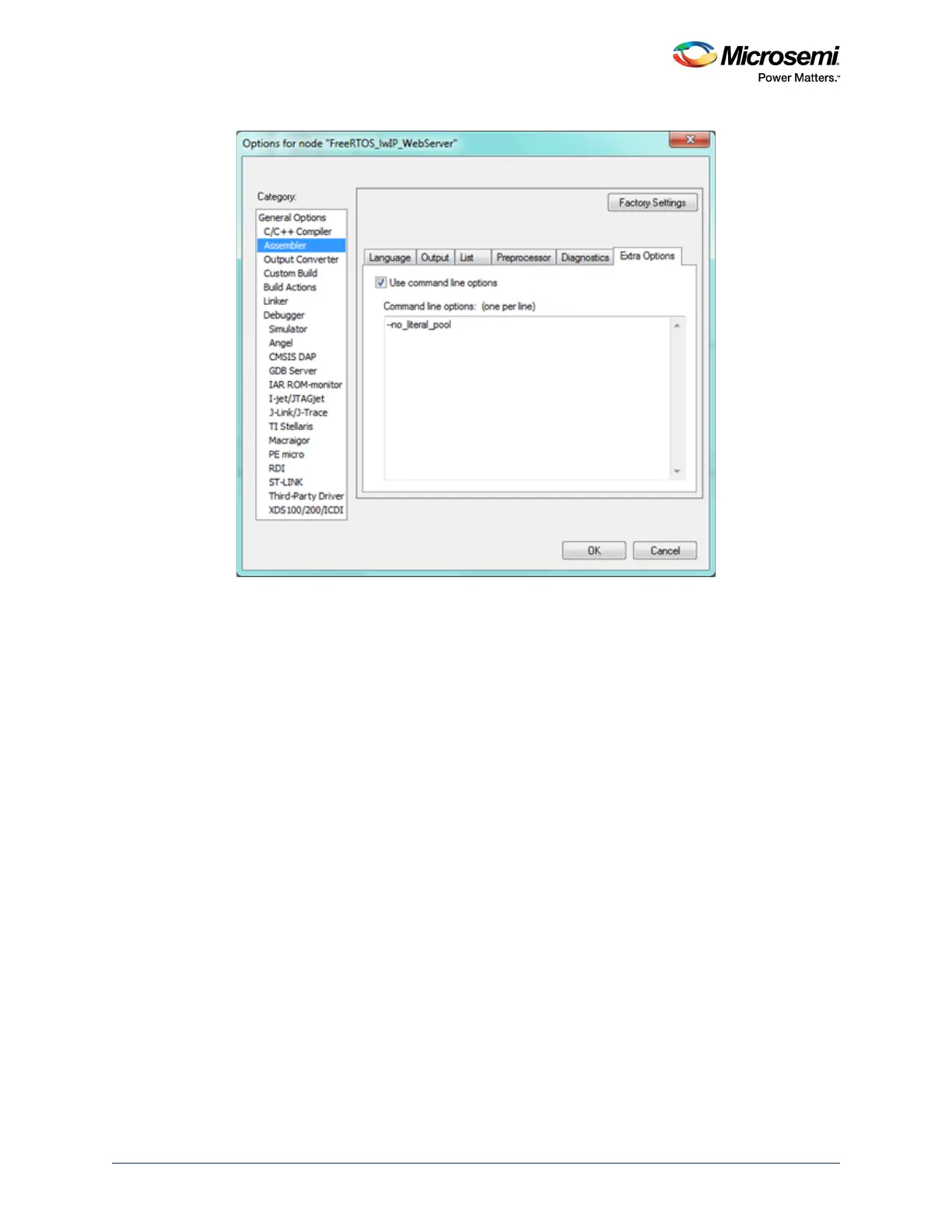

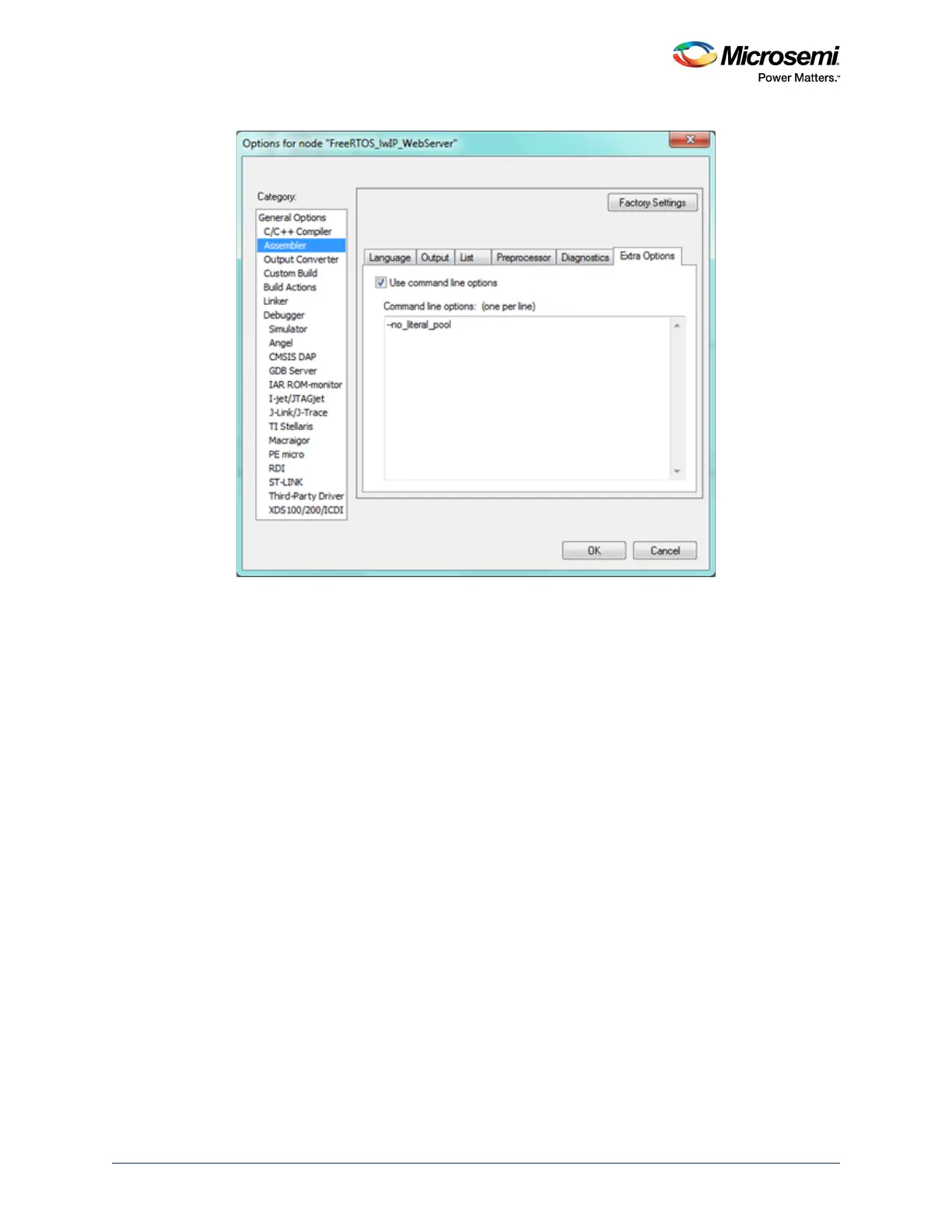

Figure 60 • IAR Assembler Options

4.2.4 Cache Locked Mode

Cache Locked mode is a special mode that provides predictable execution required for some specific

applications like avionics and certain security applications. Before enabling Cache Locked mode, the

software should ensure that the code is copied to the Cache Memory by simulating a sequential location

cache miss through DCode or writes through SBUS by enabling SBUS Write mode. After copying the

complete the 8 KB, Cache Locked mode is enabled. After Cache Locked mode is enabled, any access

from 0 to 8 KB is directly read from the cache and the cache is not invalidated or refilled for normal

operations. The memory region beyond 8 KB is treated as non-cacheable and accessed as per the

prevailing memory map.

In Cache Locked mode if an uncorrectable error is detected for cacheable address (0 to 8 KB), then the

cache line is fetched from the main memory using the cache lock base address and the entire cache line

in Cache Memory is replaced with new data from main memory. Cache Locked mode can only be used in

either DDR or eNVM remap modes and the lock base address should be used in the code region of CM3.

In Cache Locked mode the least recently used (LRU) cache update algorithm will be deactivated.

Note: CC_CACHE_LOCK bit of CC_CR system register (Ta b le 66 0, page 687) is used to lock or unlock the

entire 8 KB of Cache memory.

Loading...

Loading...