High Performance DMA Controller

UG0331 User Guide Revision 15.0 238

8.2.0.1 Interfaces

There are two types of interfaces used for communicating with HPDMA:

• 32-bit APB slave interface for configuration

• Two AHB master interfaces (AHB-M1, AHB-M2) for data transfers:

• AHB Master 1 does the read/write transfers at the AHB bus matrix end

• AHB Master 2 does the read/write transfers at the MSS DDR bridge end

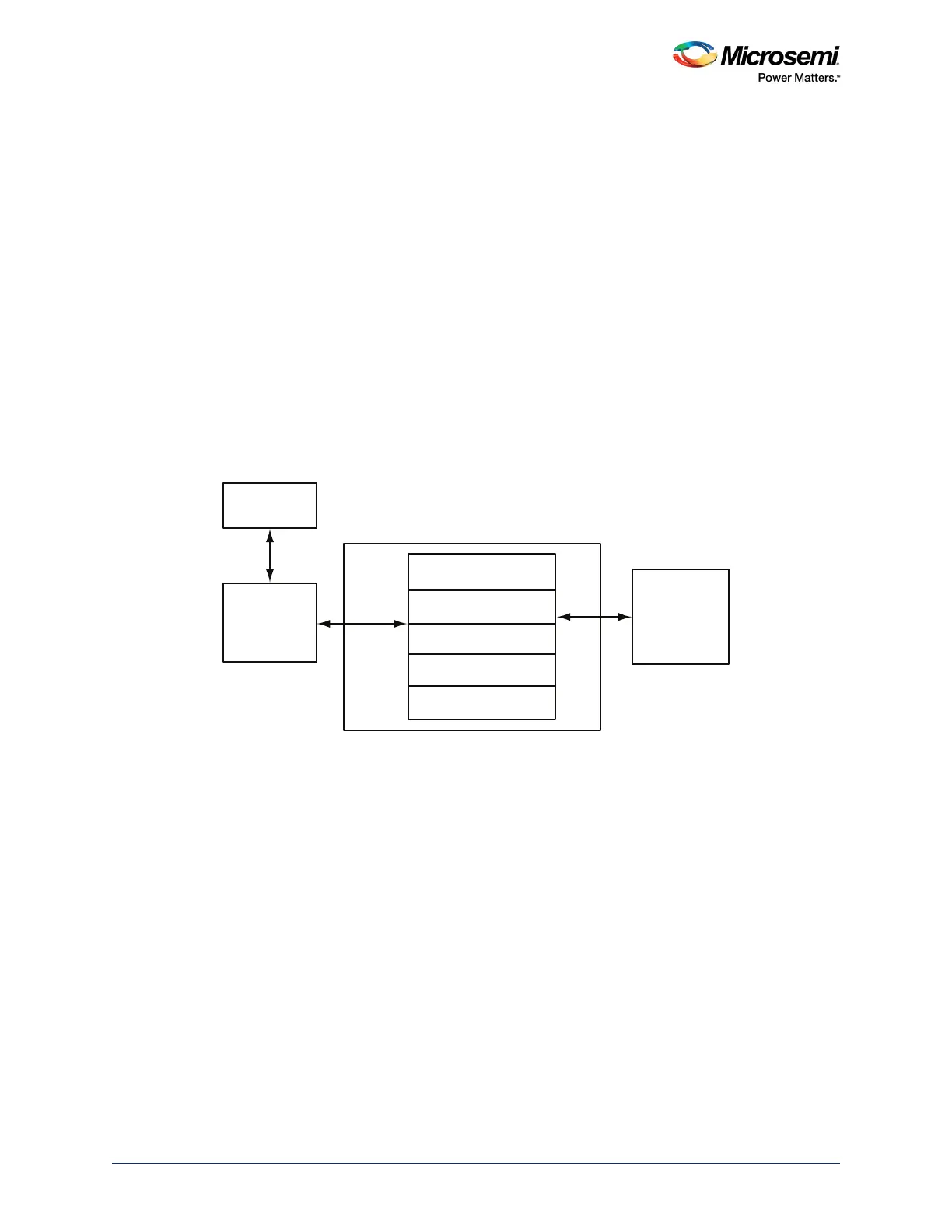

8.2.0.2 Configuration and Status Registers

The configuration and status registers of the HPDMA controller are accessed through a 32-bit APB slave,

as shown in the following figure. To enable and use HPDMA services, the AHB bus matrix master must

configure the 32-bit wide descriptor registers.

There are four descriptors available with the HPDMA controller. Each descriptor has the following five

registers:

• Source memory address register

• Destination memory address register

• Control register

• Status register

• Pending Transfer register

Figure 122 • HPDMA Registers

APB Interface

APB Slave

Descriptor 0 Registers

Descriptor 1 Registers

Descriptor 2 Registers

Descriptor 3 Registers

HPDMA Registers

Configuration and Status Registers

DMA Controller

Loading...

Loading...