Serial Peripheral Interface Controller

UG0331 User Guide Revision 15.0 536

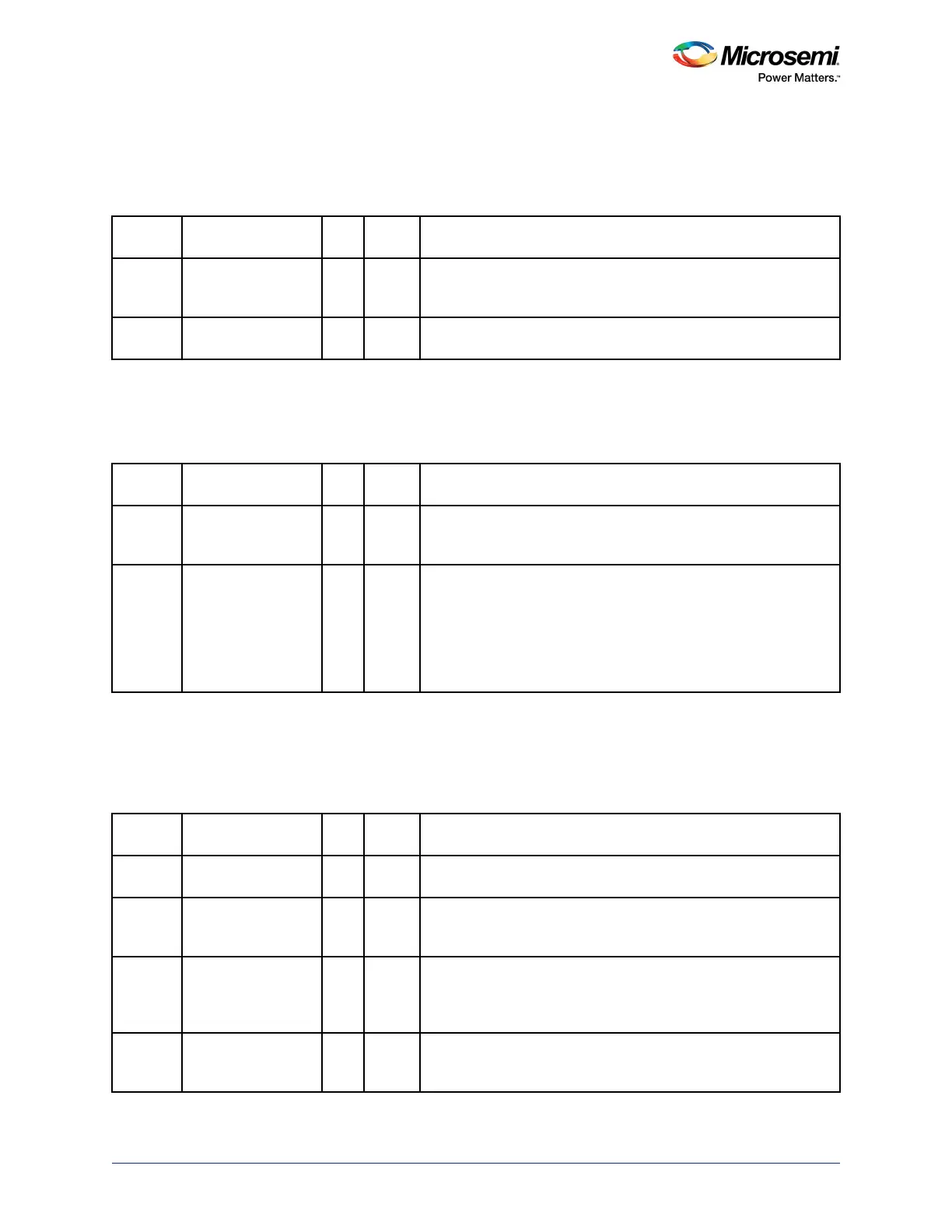

14.4.3.13 SPI Packet Size Register

The following table provides the details of the Packet Size registers that are used to set the SPI

CMD/data frame size.

14.4.3.14 SPI Command Size Register

The following table describes the Command size register.

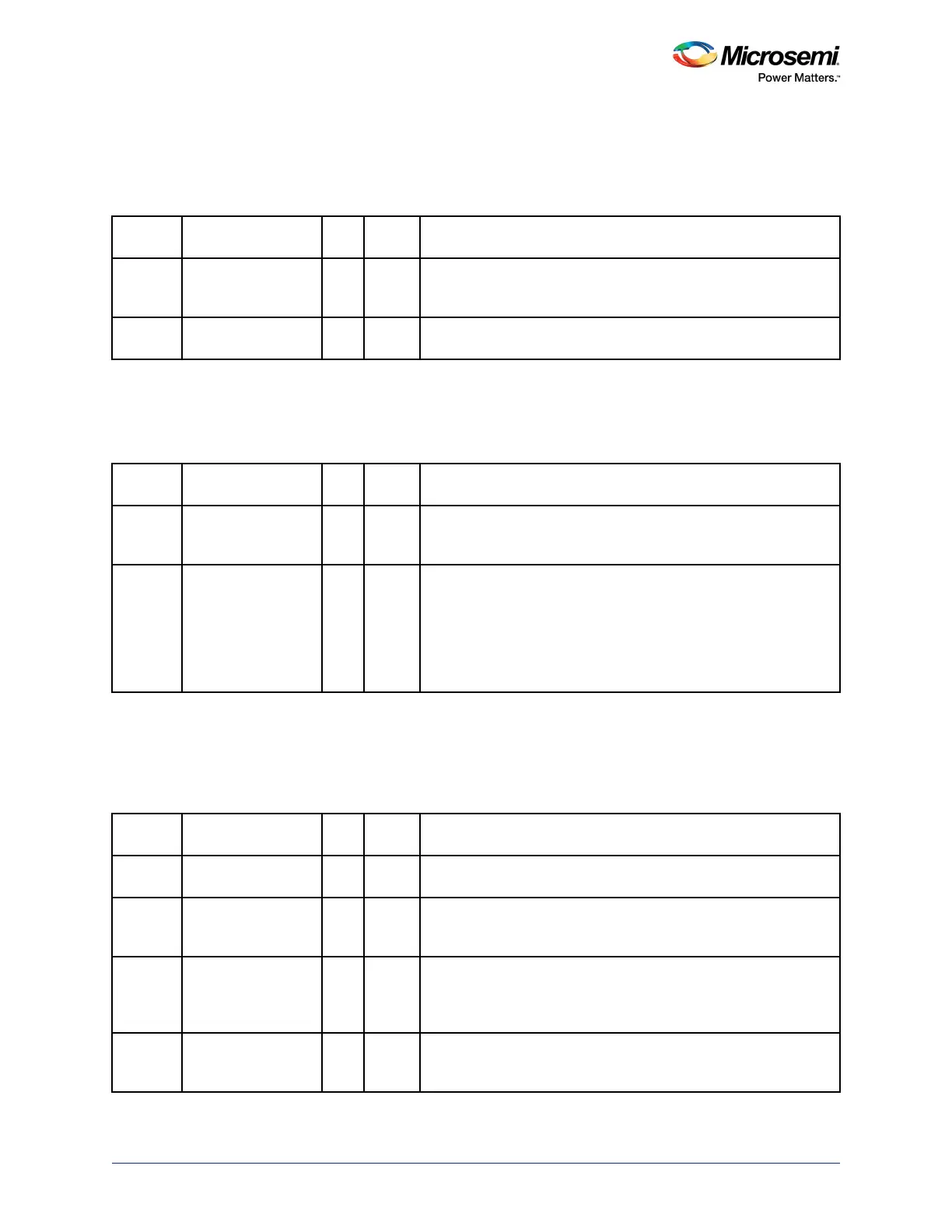

14.4.3.15 SPI Hardware Status Register

The following table describes the Hardware Status register. This register allows the Cortex-M3 processor

to control the hardware Status register used in the slave protocol controller.

Table 513 • PKTSIZE

Bit

Number Name R/W

Reset

Value Description

[31:8] Reserved R/W 0 Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should

be preserved across a read-modify-write operation.

[7:0] PKTSIZE R/W 0 Sets the size of the SPI CMD/data frame. PKTSIZE cannot be

greater than the FIFO size.

Table 514 • CMD_SIZE

Bit

Number Name R/W

Reset

Value Description

[31:8] Reserved R/W 0 Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should

be preserved across a read-modify-write operation.

[7:0] CMDSIZE R/W 0 Number of frames after SPI_SS[0] going active that the CMD

interrupt should be generated.

This controls the RxCMD interrupt. The internal counters count

frames from SPI_SS[0] going low. It automatically resets and starts

counting again once SSEL goes inactive. In TI mode, back- to-back

frames are counted, any gaps in data causes the counter to start

counting again.

Table 515 • HWSTATUS

Bit

Number Name R/W

Reset

Value Description

[31:4] Not used R/W 0 These bits are undefined. The value that the slave transmits

depends on the data that is queued in the transmit FIFO.

[3:2] USER R/W 0 These bits are set by the CPU. Their function is undefined but

could be used to send additional status or request information to

the master.

1 TXBUSY R/W 0 0: Master may request the requested data. There are PKTSIZE

frames of data in the transmit FIFO (when AUTOPOLL is set to

PKTSIZE - 1)

1: Indicates not ready to transmit data.

0 RXBUSY R/W 0 1: Indicates that the receive buffer is busy (not empty).

0: Indicates that up to PKTSIZE frames of command followed by

data may be sent to the slave.

Loading...

Loading...