Ethernet MAC

UG0331 User Guide Revision 15.0 411

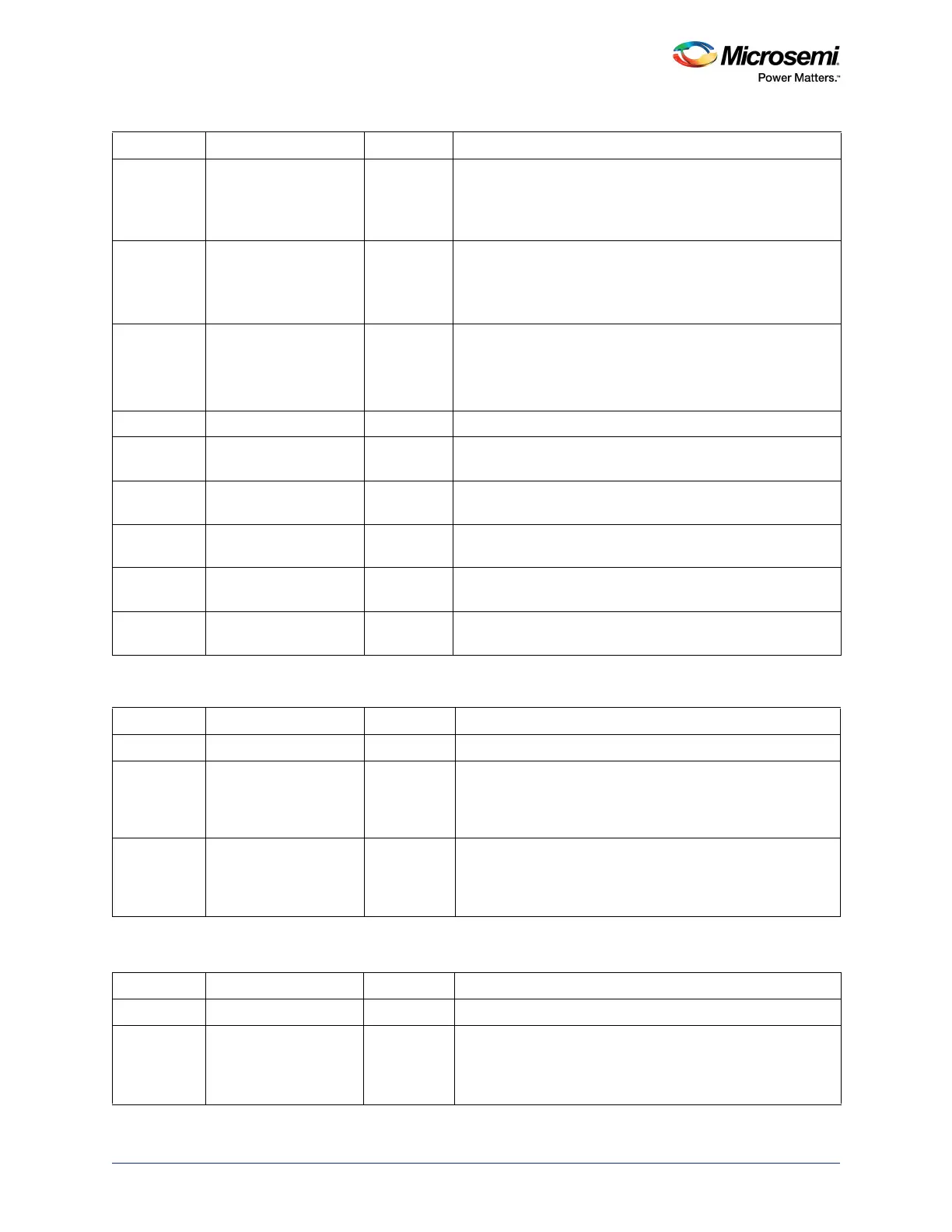

10 frfenreq 0x0 When asserted, this bit requests for enabling the FIFO fabric

receive interface module.

When de-asserted, this bit requests for disabling of the FIFO

fabric receive interface module.

9 srfenreq 0x0 When asserted, this bit requests for enabling the FIFO

PE-MCXMAC receive interface module.

When de-asserted, this bit requests for disabling the FIFO

PE-MCXMAC receive interface module.

8 wtmenreq 0x0 When asserted, this bit requests for enabling the FIFO

PE-MCXMAC Watermark module.

When de-asserted, this bit requests for disabling the FIFO

PE-MCXMAC watermark module.

[7:5] Reserved 0x0 Reserved

4 hstrstft 0x0 When asserted, this bit places the FIFO Fabric transmit

interface module in reset.

3 hstrstst 0x0 When asserted, this bit places the FIFO PE-MCXMAC

transmit interface module in reset.

2 hstrstfr 0x0 When asserted, this bit places the FIFO Fabric receive

interface module in reset.

1 hstrstsr 0x0 When asserted, this bit places the FIFO PE-MCXMAC

receive interface module in reset.

0 hstrstwt 0x0 When asserted, this bit places the FIFO PE-MCXMAC

watermark module in reset.

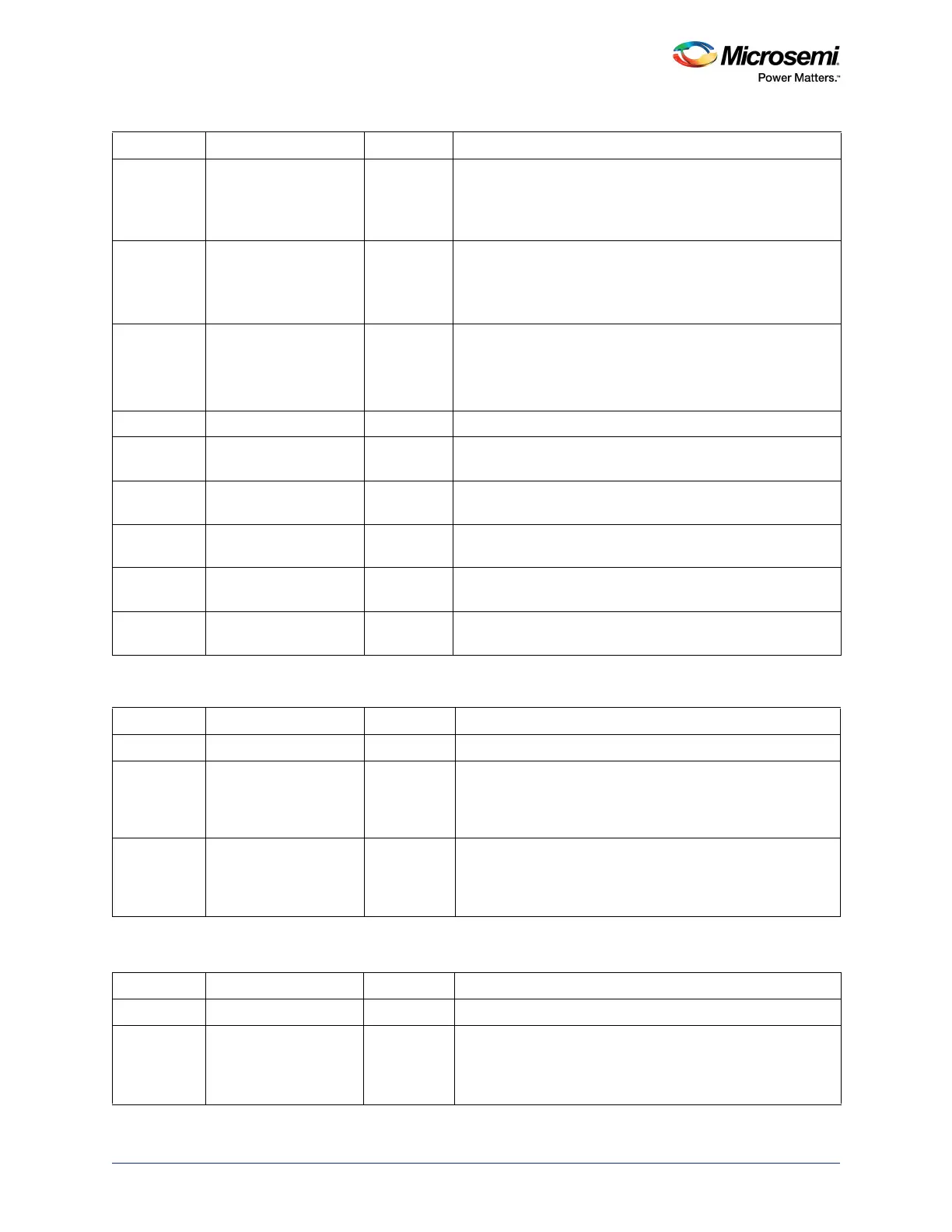

Table 364 • FIFO_CFG1

Bit Number Name Reset Value Description

[31:28] Reserved 0x0 Reserved

[27:16] cfgsrth[11:0] 0xFFF This bit represents the minimum number of 4 byte locations,

which are simultaneously stored in the receive RAM, relative

to the beginning of the frame being input, before the fabric

receive ready may be asserted.

[15:0] cfgxoffrtx 0xFFFF This bit represents the number of pause quanta after an

XOFF pause frame is acknowledged, until the A-MCXFIFO

re-asserts pause request if the A-MCXFIFO receive storage

level remains higher than the low watermark.

Table 365 • FIFO_CFG2

Bit Number Name Reset Value Description

[31:29] Reserved 0x0 Reserved

[28:16] cfghwm 0x1FFF This bit represents the maximum number of 4 byte words that

are simultaneously stored in the receive RAM before the

transmit flow control enables and pause value facilitates an

XOFF pause control frame.

Table 363 • FIFO_CFG0 (continued)

Bit Number Name Reset Value Description

Loading...

Loading...