Communication Block

UG0331 User Guide Revision 15.0 594

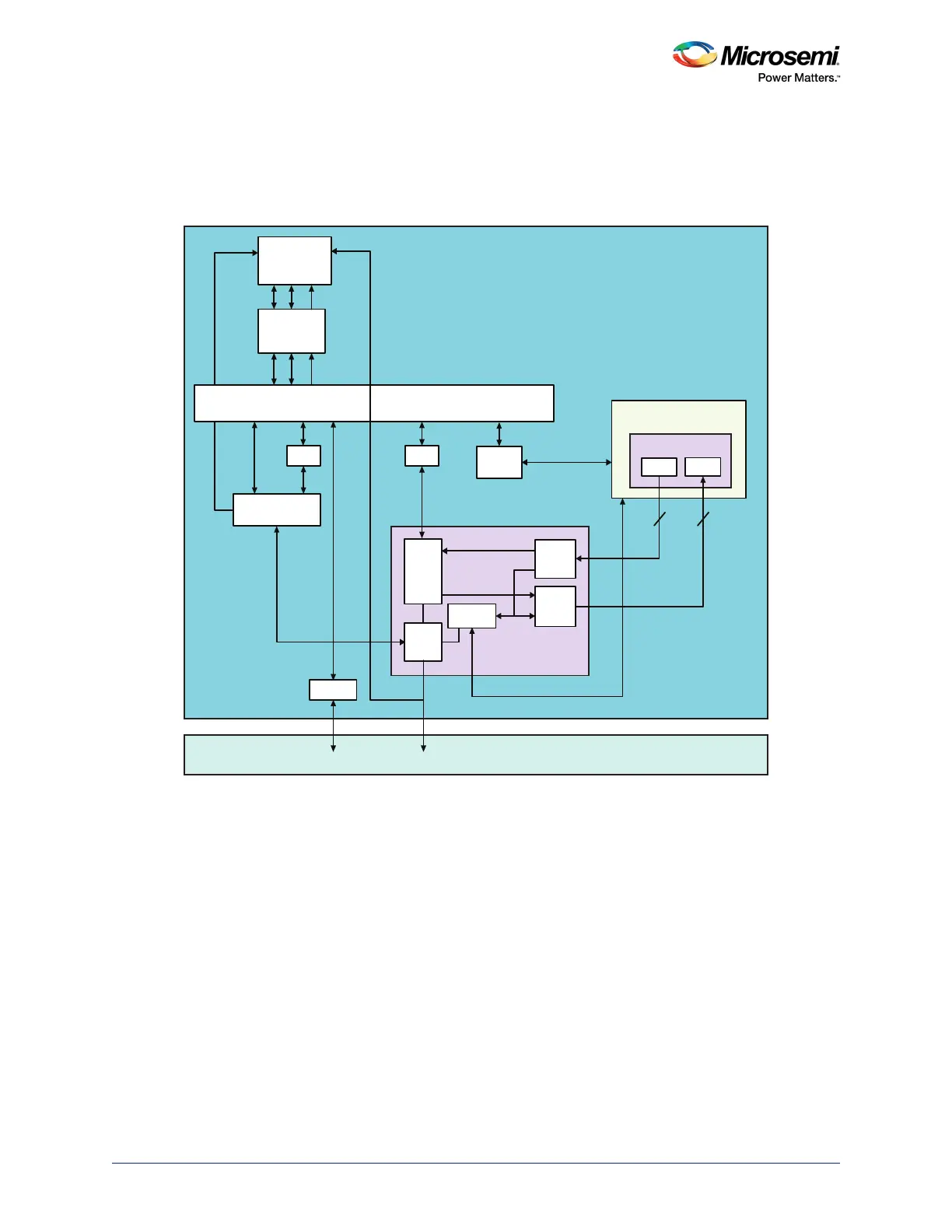

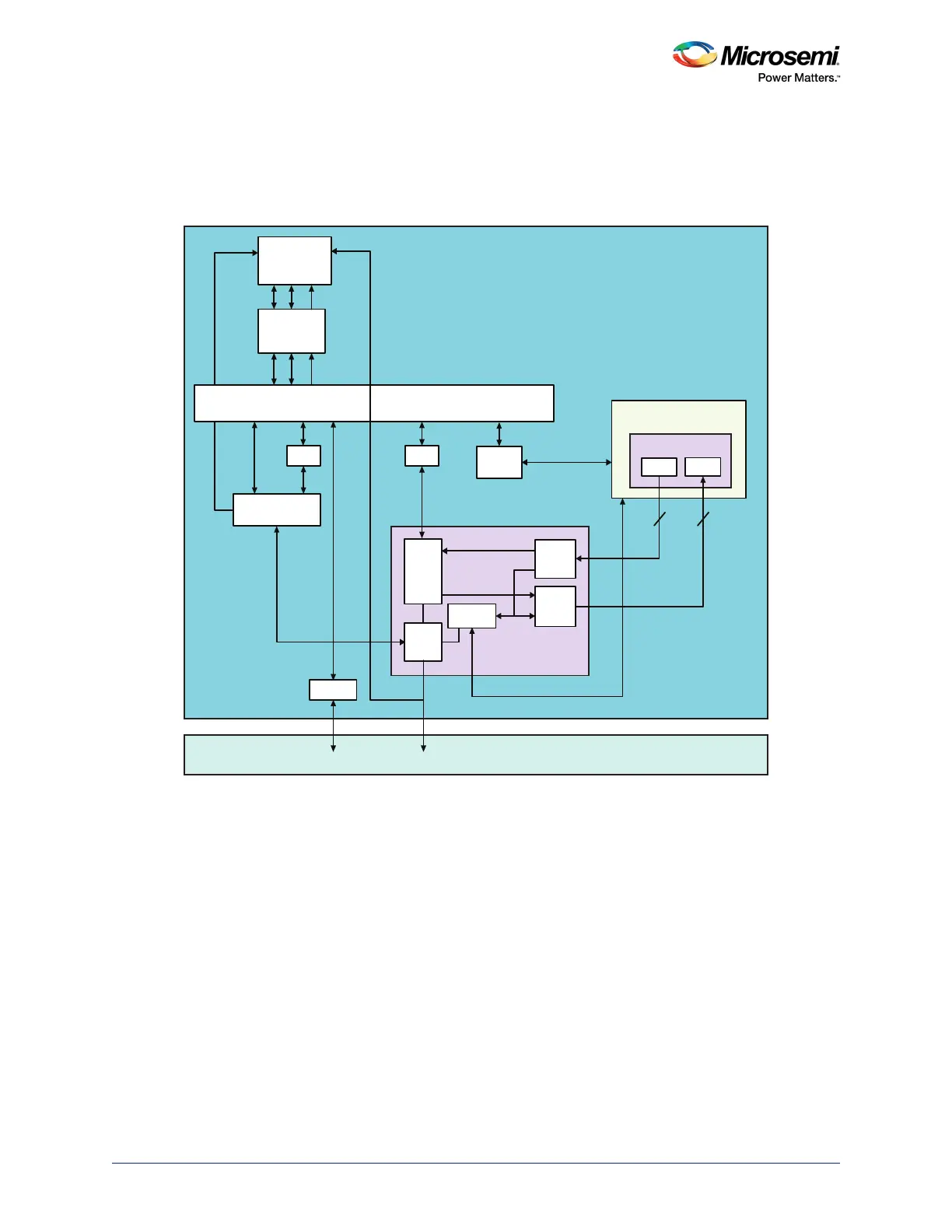

In the other direction, the interrupt (COMM_BLK_INT) goes to both the Cortex-M3 processor and the

FPGA fabric through the fabric interface interrupt controller (FIIC). This communication link is used as a

message passing mailbox by firmware running on the Cortex-M3 processor and system controller. The

following figure shows how COMM_BLKs are connected to create a communication channel between the

Cortex-M3 processor and the system controller.

Figure 251 • Interfacing of COMM_BLK with System Controller

The COMM_BLK supports PDMA operation. The peripheral ready signals, RxRDY and TxRDY are

directly connected to the PDMA, and are used for flow control between the MSS COMM_BLK and PDMA

channel. Data from the COMM_BLK receive FIFO going to any MSS memory mapped locations, and the

data from any MSS memory mapped locations going to the COMM_BLK transmit FIFO can be

transferred without using the Cortex-M3 processor or the system controller. The PDMA supports DMA

transfers from embedded nonvolatile memory (eNVM) to the COMM_BLK to facilitate the initialization of

fabric SRAMs—Micro SRAM (uSRAM) and Large SRAM (LSRAM).

17.2.2 Frame/Command Marker

The COMM_BLK allows the data that is being transferred to be marked as a command or data byte. It is

expected that a software protocol transfers packets of data between the COMM_BLK blocks. To allow the

receiver to correctly identify the start of a packet, the COMM_BLK block uses a 9th bit (Bit 8 of DATA_IN

and DATA_OUT as shown in Figure 251 on page 594).

When FRAME_START8/FRAME_START32 register is written, the 9th bit is set. When DATA8/DATA32

register is written, the 9th bit is not set.

The STATUS register bit 7 gives indication to the receiver whether the next byte that will be read out of

the FIFO has the 9th bit set, and therefore indicating that it is the start of a packet.

AHB Bus Matrix

Cache

Controller

SD IC

ARM Cortex - M3

SD I

APB_1

PDMA

RxRDY

&

TxRDY

APB_0

COMMS_INT

TX FIFO

RX FIFO

SII Interface

Control &

Status

APB

Interface

COMM

_

BLK

AHB

SII Master

SII Bus

MSS

FABRIC

FIC

DATA_IN [8:0]*

DATA_OUT [8:0]*

9

9

* 9th bit is used as a start of

frame (command) marker

TX FIFO RX FIFO

COMM

_

BLK

System Controller

Processor

PDMA INTERRUPT

Loading...

Loading...