Embedded NVM (eNVM) Controllers

UG0331 User Guide Revision 15.0 182

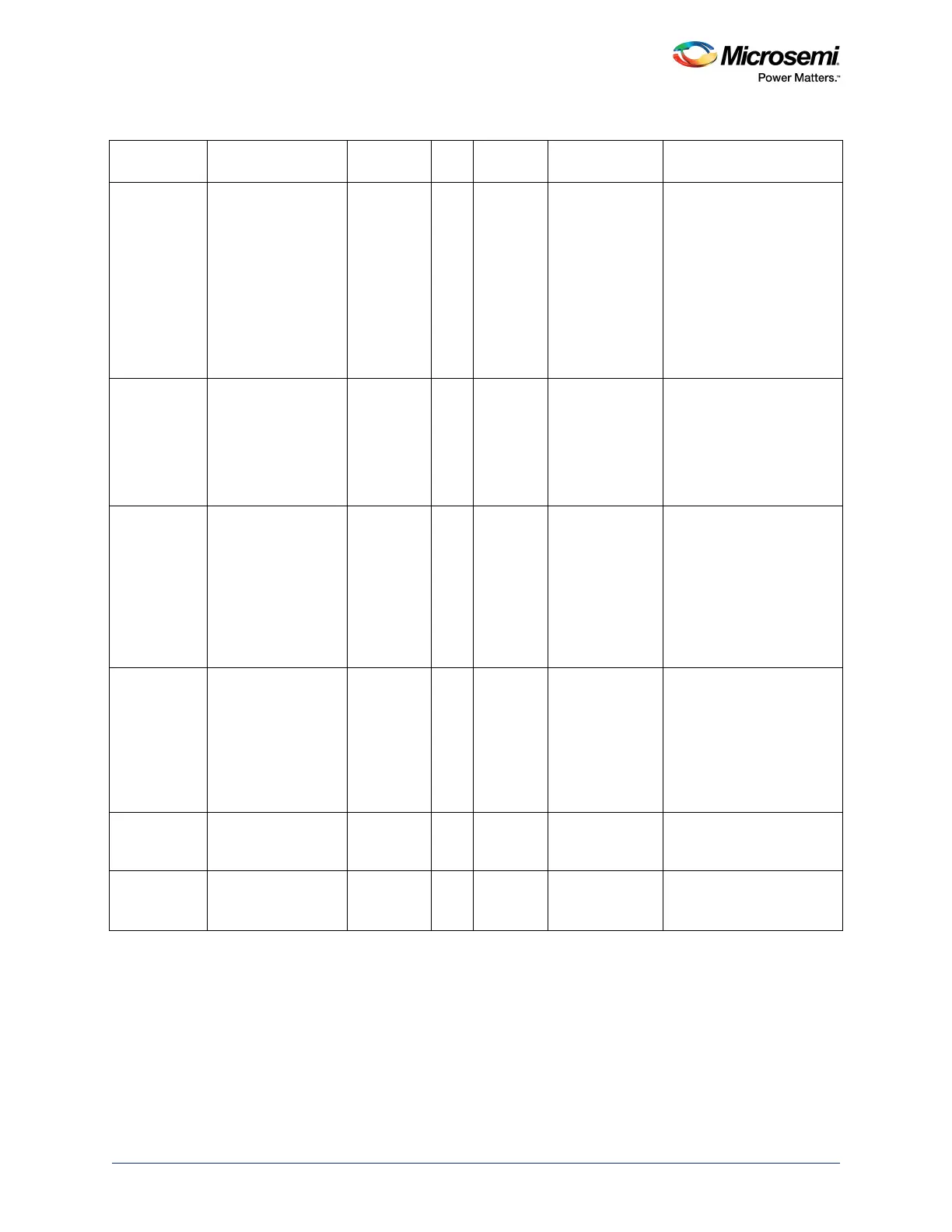

0x134 NV_CE 2-bit R/W 1 Exclusive access

to the requested

master

NV_CE[0] = 0: NVM

disabled

NV_CE[0] = 1: NVM

enabled

NV_CE [1] = 1; The internal

read cache is disabled. All

reads will directly read the

eNVM array, or AB space.

When set NVM access

latency will increase. By

default this bit is set to '0'.

0x140 PAGE_LOCK_SET 1 R/W 0 Exclusive access

to the requested

master

PAGE_LOCK_SET[0] = 1:

Page is locked.

PAGE_LOCK_SET[0] = 0:

Page is unlocked.

If the page is locked, then

before writing the page

should be unlocked.

0x144 DWSIZE 3:0 R/W 0 Exclusive access

to the requested

master

Write size in number of

double words, to be written

to assembly buffer from

Write Data buffer during

NVM commands. See

description for individual

commands.

0000 = 1 dword

1111 = 16 dwords

0x148 CMD 31:0 R/W 0 Exclusive access

to the requested

master

Write to CMD and if

command field in HWDATA

decoded to be a command,

then NVM command will be

initiated. See description of

Table 103, page 174: CMD

register and individual

commands.

0x154 INTEN[10:0] 10:0 R/W 0 Exclusive access

to the requested

master

Writing '1' to each bit will

enable the corresponding

interrupt.

0x158 CLRHINT[2:0] 2:0 W 0 Exclusive access

to the requested

master

Clear interrupts/flag/busy bit

by writing 1 to the

corresponding bit.

Table 112 • Control Registers Description (continued)

OFFSET

HADDR[8:0] Register Name Width Type Default Access Rights Description

Loading...

Loading...