Cortex-M3 Processor (Reference Material)

UG0331 User Guide Revision 15.0 42

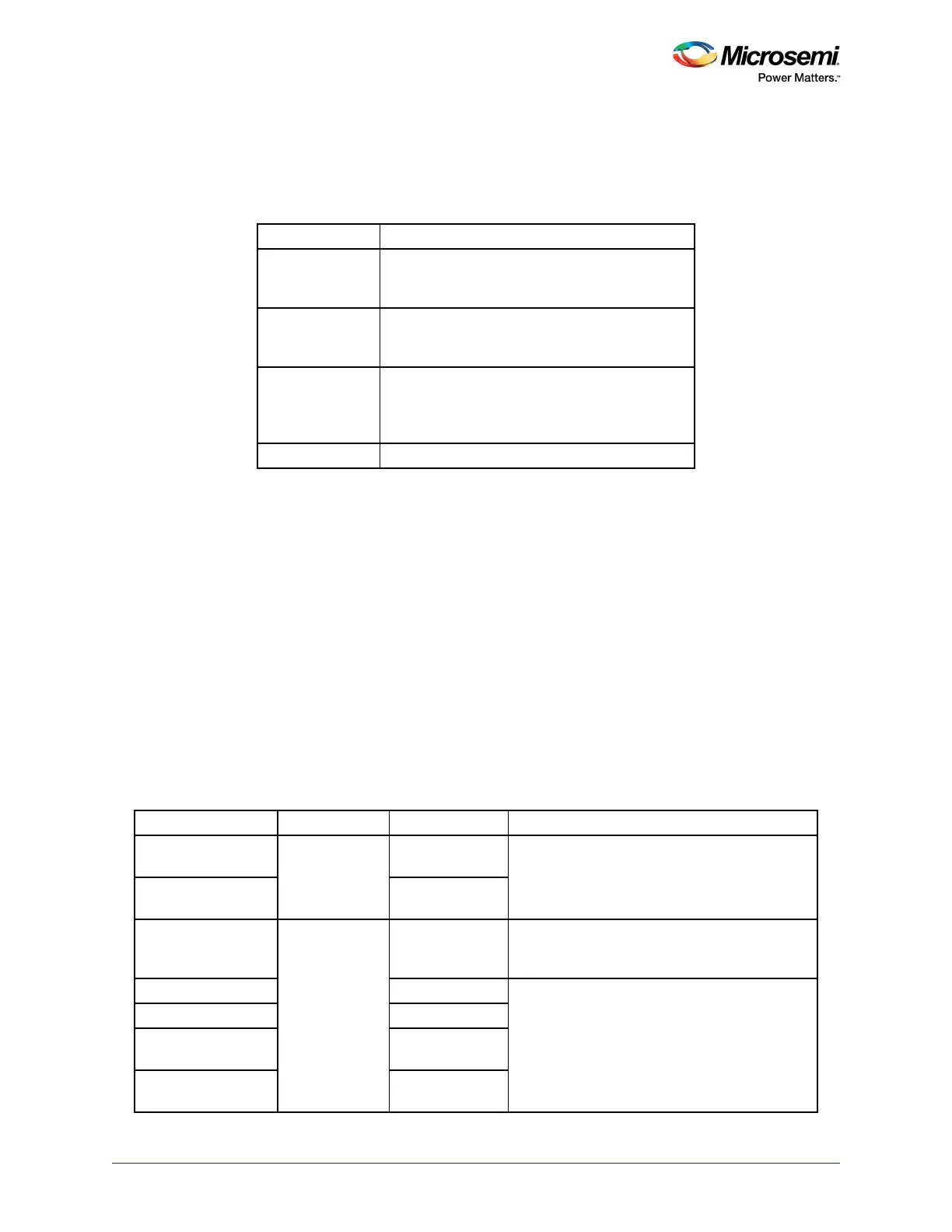

When the processor loads a value matching this pattern to the PC it detects that the operation is a not a

normal branch operation and, instead, that the exception is complete. Therefore, it starts the exception

return sequence. Bits[3:0] of the EXC_RETURN value indicate the required return stack and processor

mode, as noted in the following table

.

3.5.4 Fault Handling

Faults are a subset of the exceptions, see Exception Model, page 37. The following generates a fault:

• a bus error on:

• an instruction fetch or vector table load

• a data access

• an internally-detected error such as an undefined instruction

• attempting to execute an instruction from a memory region marked as Non-Executable (XN).

• attempting to execute an instruction while the EPSR T-bit is clear. For example, as the result of an

erroneous

BX

instruction, or a vector fetch from a vector table entry with bit[0] clear.

• an MPU fault because of a privilege violation or an attempt to access an unmanaged region.

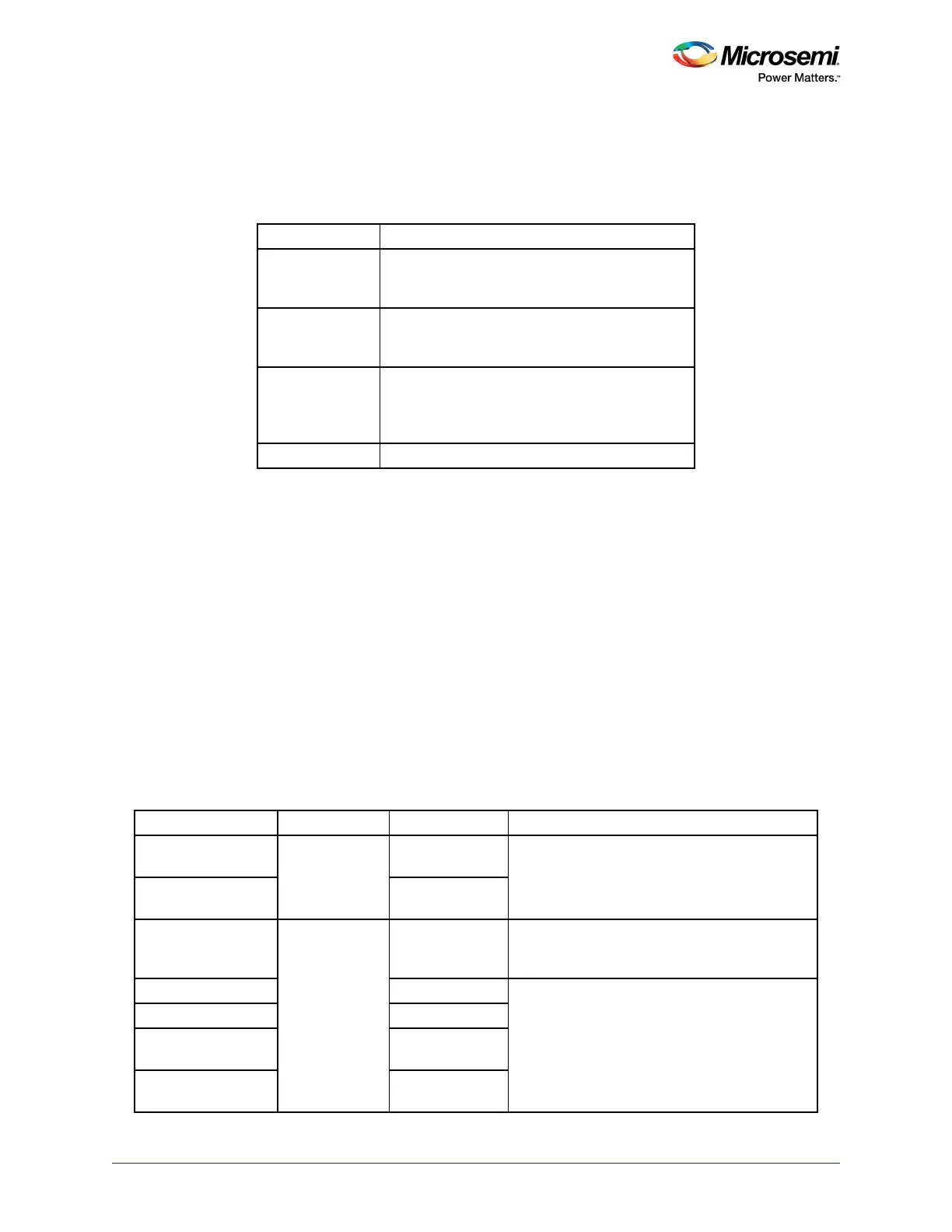

3.5.4.1 Fault Types

The following table shows the types of fault, the handler used for the fault, the corresponding fault status

register, and the register bit that indicates that the fault has occurred. See Configurable Fault Status

Register, page 113 for more information about the fault status registers.

Table 23 • Exception Return Behavior

EXC_RETURN Description

0xFFFFFFF1 Return to Handler mode.

Exception return gets state from the main stack.

Execution uses MSP after return.

0xFFFFFFF9 Return to Thread mode.

Exception Return get state from the main stack.

Execution uses MSP after return.

0xFFFFFFFD Return to Thread mode.

Exception return gets state from the process

stack.

Execution uses PSP after return.

All other values Reserved.

Table 24 • Faults

Fault Handler Bit name Fault status register

Bus error on a vector

read

HardFault VECTTBL HardFault Status Register

Fault escalated to a

HardFault

FORCED

MPU or default

memory map

mismatch:

MemManage

on instruction access IACCVIOL

1

MemManage Fault Status Register

on data access DACCVIOL

during exception

stacking

MSTKERR

during exception

unstacking

MUNSKERR

Loading...

Loading...