Universal Serial Bus OTG Controller

UG0331 User Guide Revision 15.0 331

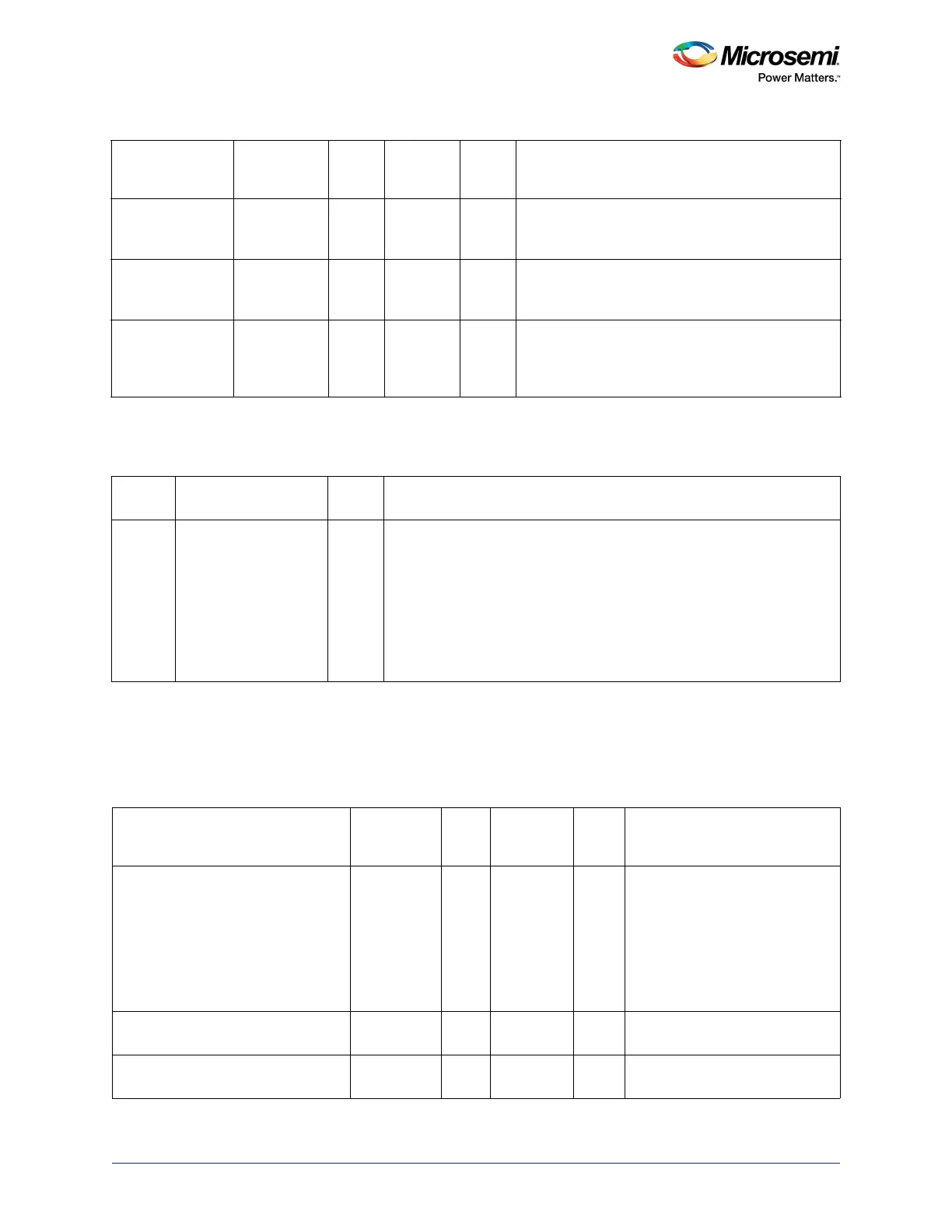

10.3.7.1 EPx_FIFO_REG Bit Definitions

10.3.8 Control and Status Registers (OTG, Dynamic FIFO and Version)

This section covers all registers in this category along with the address offset, functionality, and per bit

details.

EP2_FIFO_REG 0x0028 32 RW 0 Writing to this address loads data into the endpoint2

transmit FIFO. Reading from this address unloads

data from the endpoint2 transmit FIFO.

EP3_FIFO_REG 0x002C 32 RW 0 Writing to this address loads data into the endpoint3

transmit FIFO. Reading from this address unloads

data from the endpoint3 transmit FIFO.

EP4_FIFO_REG 0x0030 32 RW 0 Writing to this addresses loads data into the

endpoint4 transmit FIFO. Reading from this

address unloads data from the endpoint4 transmit

FIFO.

Table 239 • EPx_FIFO_REG (0x400430YZ)

Bit

Number Name

Reset

Value Function

[31:0] Epx_TxRxDataAcc 0 Address of endpointx to write data into transmit FIFO or read from

receive FIFO.

The value of x can be 0, 1, 2, 3, or 4.

The values of YZ would be differ with the register name:

1. EP0_FIFO_REG - 0x40043020

2. EP1_FIFO_REG - 0x40043024

3. EP2_FIFO_REG - 0x40043028

4. EP3_FIFO_REG - 0x4004302C

5. EP4_FIFO_REG - 0x40043030

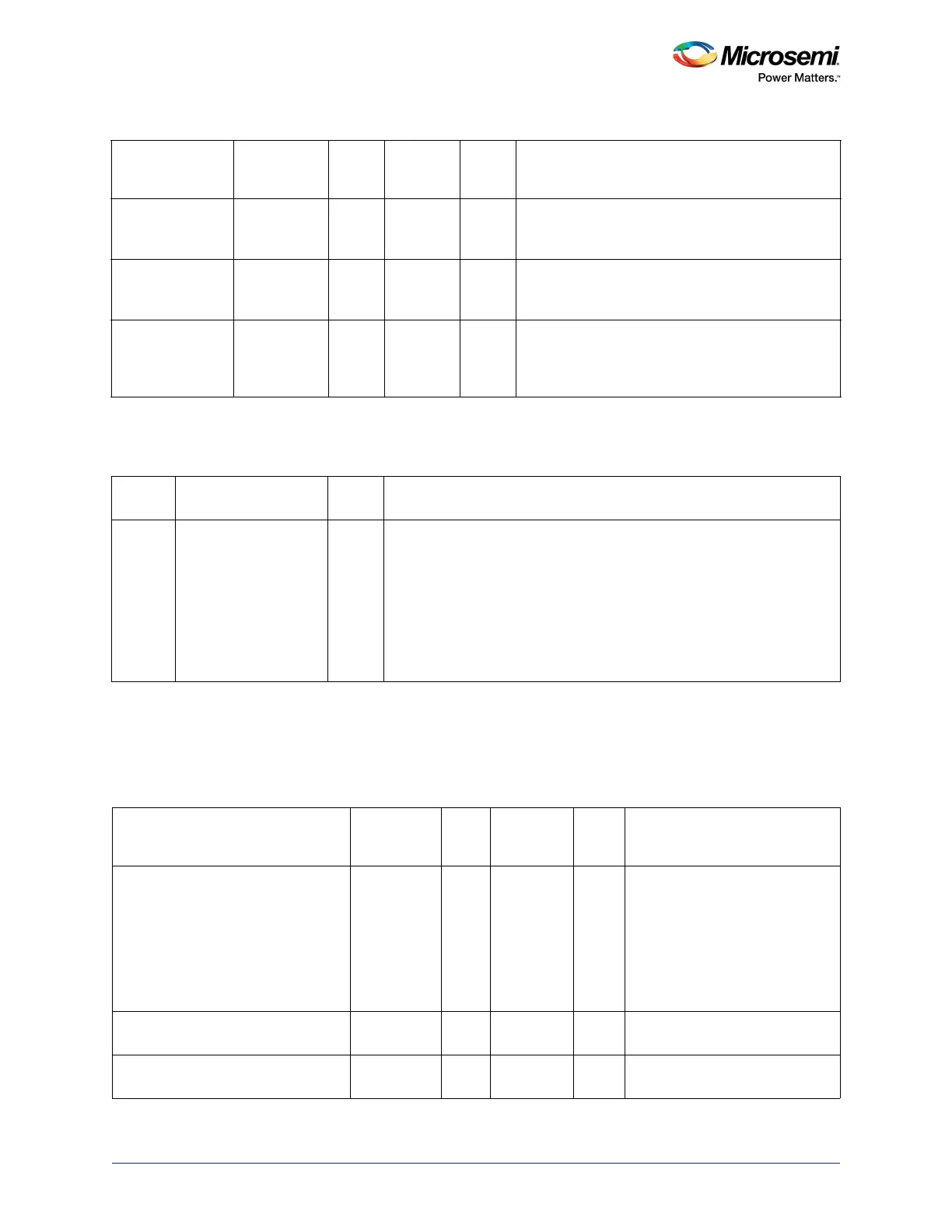

Table 240 • Additional Control and Status Registers (OTG, Dynamic FIFO, and Version)

Register Name

Address

Offset from

0x40043000 Width R/W Type

Reset

Value Description

DEV_CTRL_REG (0x40043060) 0x0060 8 R 0x80 Selects whether the USB

controller is operating in

Peripheral mode or in Host mode,

and for controlling and monitoring

the USB VBus line. If the PHY is

suspended, no PHY clock (XCLK)

is received and the VBus is not

sampled.

MISC_REG (0x40043061) 0x0061 8 R 0 Contains the early DMA enable

bits for receive and transmit.

TX_FIFO_SIZE_REG (0x40043062) 0x0062 5 RW 0 Controls the size of the selected

transmit endpoint FIFO.

Table 238 • FIFO Registers (continued)

Register Name

Address

Offset from

0x40043000 Width R/W Type

Reset

Value Description

Loading...

Loading...