System Register Block

UG0331 User Guide Revision 15.0 701

Note: Do not change these register fields dynamically for 005 and 010 devices, see System Registers Behavior

for M2S005/010 Devices, page 682.

22.3.32 USB Configuration Register

22.3.33 eSRAM PIPELINE Configuration Register

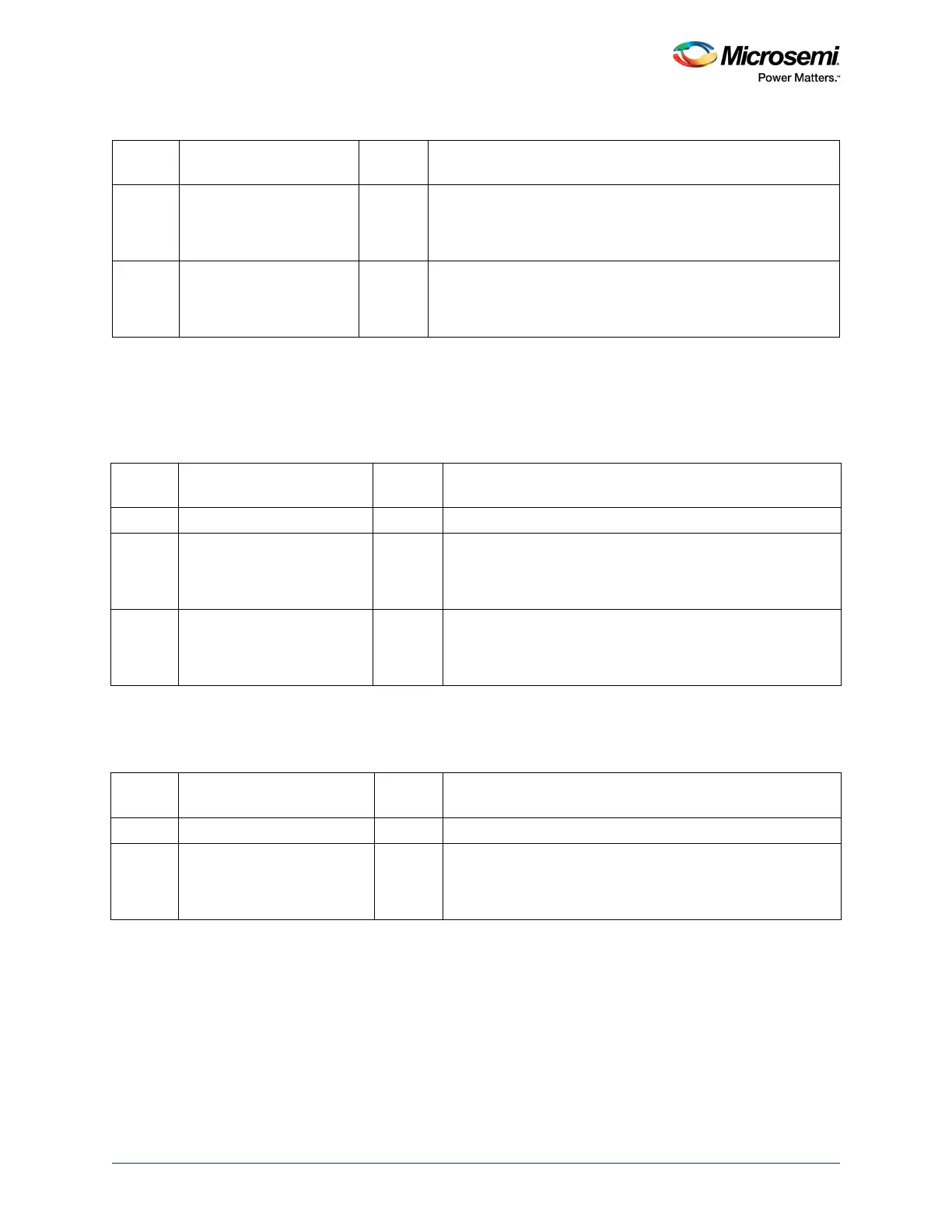

1 ESRAM0_EDAC_2E_EN 0 Allows the 2-bit error EDAC for eSRAM0 status update to be

disabled. Allowed values:

0: Disabled

1: Enabled

0 ESRAM0_EDAC_1E_EN 0 Allows the 1-bit error EDAC for eSRAM0 status update to be

disabled. Allowed values:

0: Disabled

1: Enabled

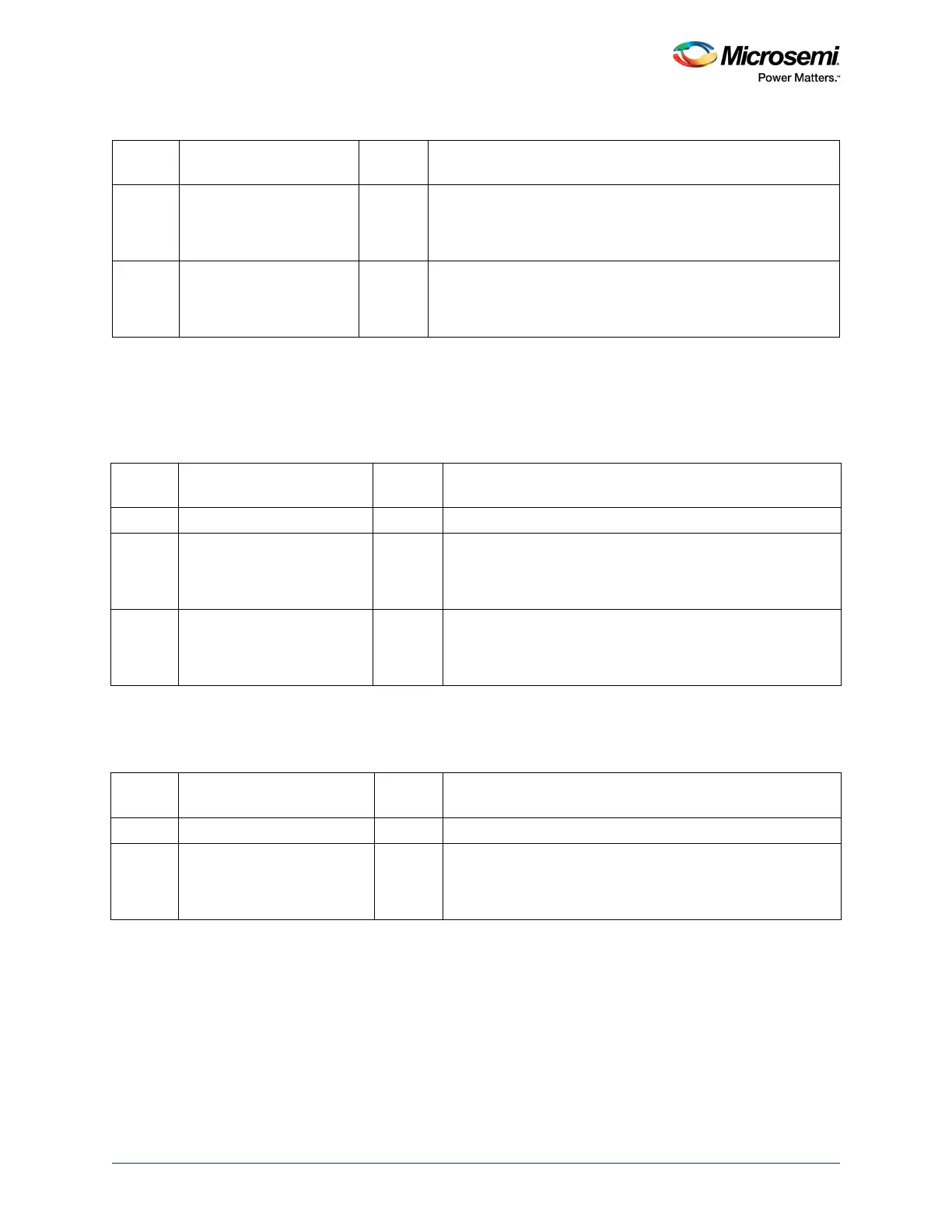

Table 686 • USB_CR

Bit

Number Name

Reset

Value Description

[31:2] Reserved 0

1 USB_DDR_SELECT 0 Used to configure USB works in single data rate (SDR) mode or

double data rate (DDR) mode. Allowed values:

0: SDR mode is selected

1: DDR mode is selected

0 USB_UTMI_SEL 0 Used to configure the USB interface as ULPI PHY or UTMI

interface. Allowed values:

0: ULPI PHY interface is selected

1: UTMI interface is selected

Table 687 • ESRAM_PIPELINE_CR

Bit

Number Name

Reset

Value Description

[31:1] Reserved 0

0 ESRAM_PIPELINE_ENABLE 0x1 Controls the pipeline in the read path of eSRAM memory.

Allowed values:

0: Pipeline is bypassed

1: Pipeline is present in the memory read path

Table 685 • EDAC_IRQ_ENABLE_CR (continued)

Bit

Number Name

Reset

Value Description

Loading...

Loading...