Peripheral DMA

UG0331 User Guide Revision 15.0 275

6. Start the transfer using PDMA_start()

• Buffer A and buffer B source and destination addresses

• Transfer count in bytes

7. Enable channel interrupt and Cortex-M3 interrupt using PDMA_enable_irq().

8. Disable the interrupt for channel PDMA_disable_irq().

9. To pause the data transfers, use PDMA_pause().

10. To resume the data transfer, use PDMA_resume().

11. Check for completion of the data transfer using PDMA_status().

Note: The MSS PDMA does not support full behavioral simulation models. Refer to SmartFusion2 MSS BFM

Simulation User Guide for more information.

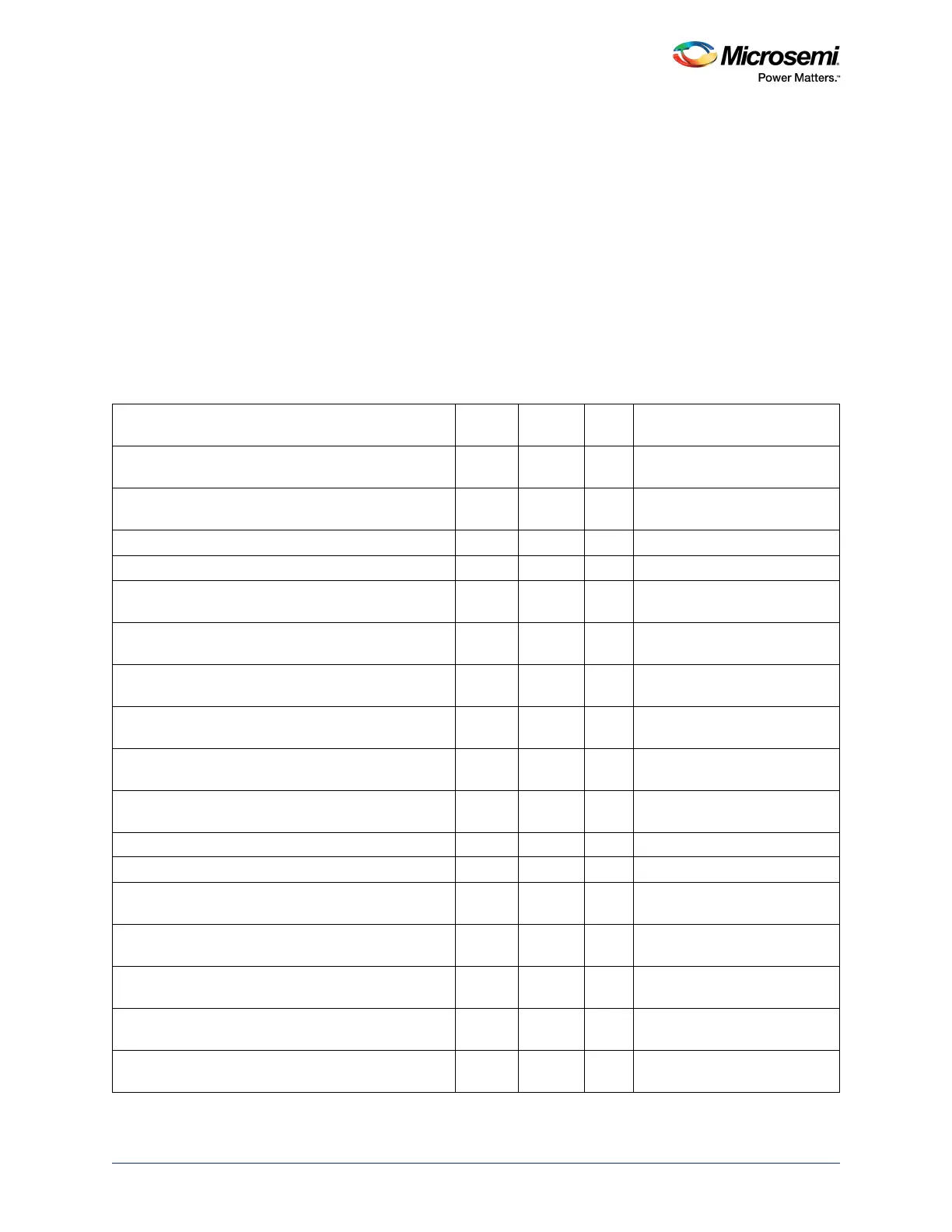

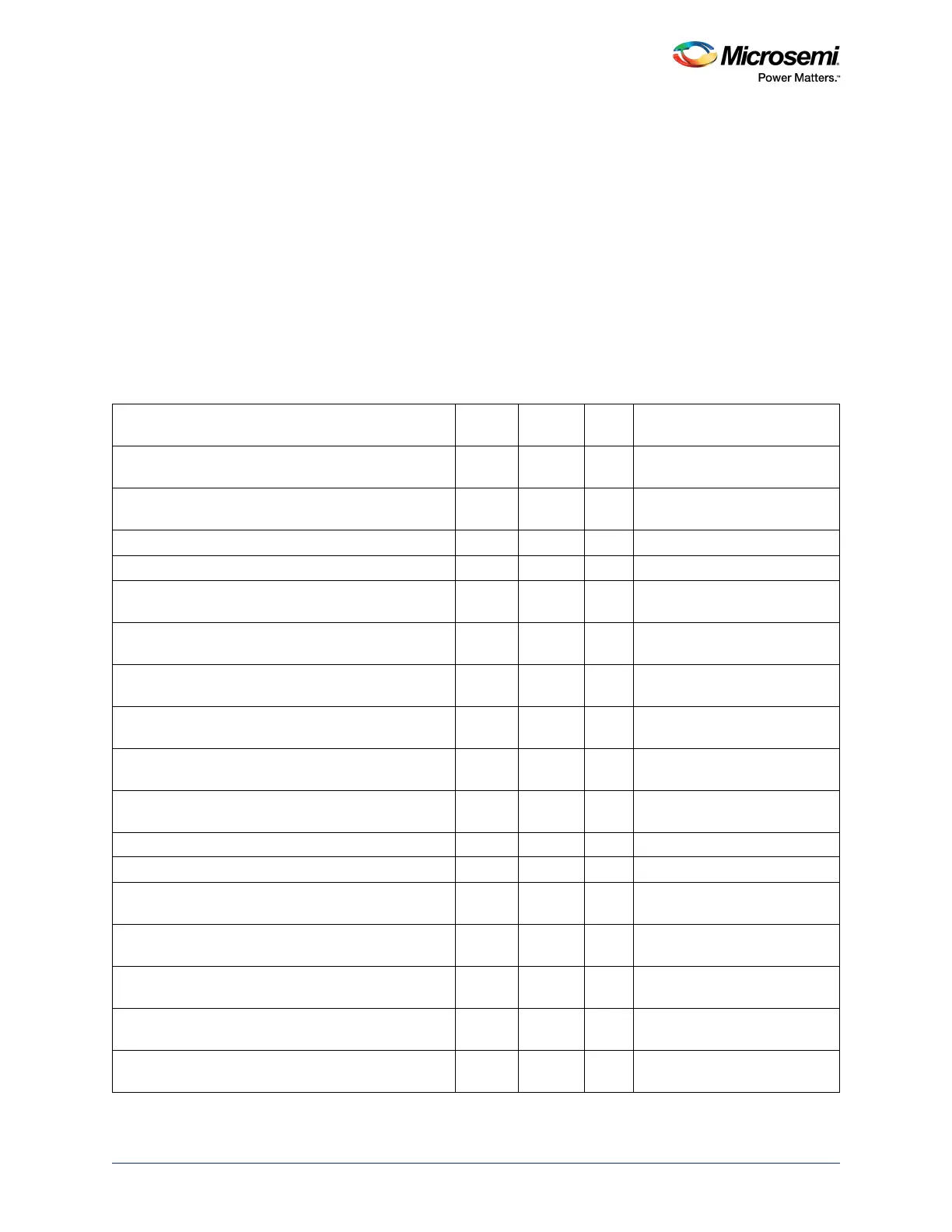

9.4 PDMA Register Map

The following table summarizes each of the registers covered by this document. The base address is

0x40003000.

Table 177 • SmartFusion2 SoC FPGA PDMA Register Map

Register Name

Address

Offset

Register

Type

Reset

Value Description

Ratio_HIGH_LOW 0x00 R/W 0 Ratio of high priority transfers

versus low priority transfers.

BUFFER_STATUS 0x04 R 0 Indicates when buffers have

drained.

CHANNEL_x_CONTROL (X=0) 0x20 R/W 0 Channel 0 Control register

CHANNEL_x_STATUS (X=0) 0x24 R 0 Channel 0 Status register

CHANNEL_x_BUFFER_A_SRC_ADDR (x=0) 0x28 R/W 0 Channel 0 buffer A source

address

CHANNEL_x_BUFFER_A_DST_ADDR (x=0) 0x2C R/W 0 Channel 0 buffer A destination

address

CHANNEL_x_BUFFER_A_TRANSFER_COUNT

(x=0)

0x30 R/W 0 Channel 0 buffer A transfer

count

CHANNEL_x_BUFFER_B_SRC_ADDR (x=0) 0x34 R/W 0 Channel 0 buffer B source

address

CHANNEL_x_BUFFER_B_DST_ADDR (x=0) 0x38 R/W 0 Channel 0 buffer B destination

address

CHANNEL_x_BUFFER_B_TRANSFER_COUNT

(x=0)

0x3C R/W 0 Channel 0 buffer B transfer

count

CHANNEL_1_CONTROL 0x40 R/W 0 Channel 1 Control register

CHANNEL_1_STATUS 0x44 R 0 Channel 1 Status register

CHANNEL_1_BUFFER_A_SRC_ADDR 0x48 R/W 0 Channel 1 buffer A source

address

CHANNEL_1_BUFFER_A_DST_ADDR 0x4C R/W 0 Channel 1 buffer A destination

address

CHANNEL_1_BUFFER_A_TRANSFER_COUNT 0x50 R/W 0 Channel 1 buffer A transfer

count

CHANNEL_1_BUFFER_B_SRC_ADDR 0x54 R/W 0 Channel 1 buffer B source

address

CHANNEL_1_BUFFER_B_DST_ADDR 0x58 R/W 0 Channel 1 buffer B destination

address

Loading...

Loading...