System Register Block

UG0331 User Guide Revision 15.0 697

Note: Do not change these register fields dynamically for 005 and 010 devices, see System Registers Behavior

for M2S005/010 Devices, page 682.

22.3.25 GPIO Input Source Select Control Register

Note: Do not change these register fields dynamically for 005 and 010 devices, see System Registers Behavior

for M2S005/010 Devices, page 682.

22.3.26 MDDR Configuration Register

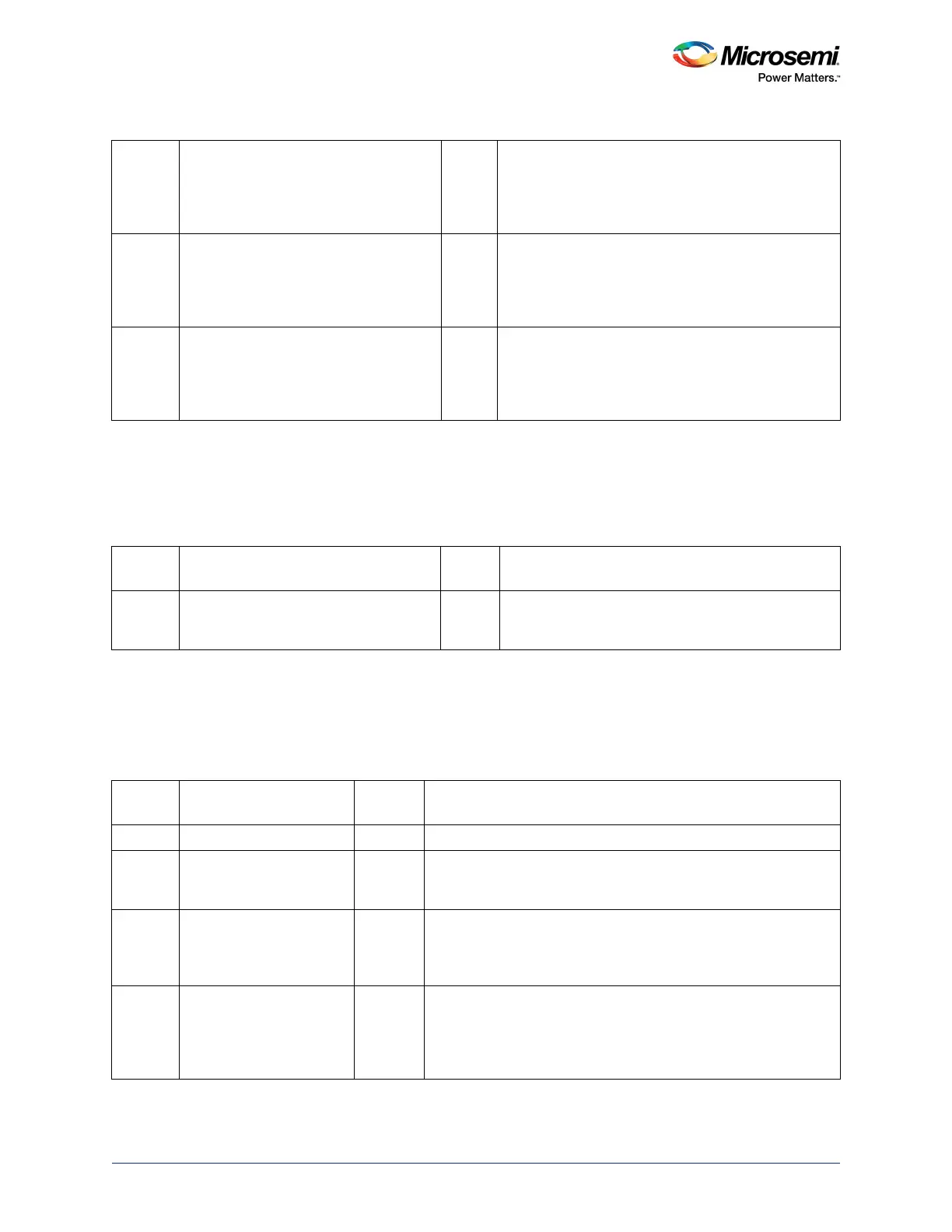

2 MSS_GPIO_23_16_SYSRESET_SEL 0 0: Selects the combination of either

power-on reset or the MSS_GPIO_RESET_N signal

from the FPGA fabric to reset the GPIO

1: Causes GPIO[23:16] to be held in reset by the soft

reset signal MSS_GPIO_23_16_SOFT_RESET

1 MSS_GPIO_15_8_SYSRESET_SEL 0 0: Selects the combination of either power-on reset or

the MSS_GPIO_RESET_N signal from the FPGA

fabric to reset the GPIO

1: Causes GPIO[15:8] to be held in reset by the soft

reset signal MSS_GPIO_15_8_SOFT_RESET

0 MSS_GPIO_7_0_SYSRESET_SEL 0 0: Selects the combination of either power-on reset or

the MSS_GPIO_RESET_N signal from the FPGA

fabric to reset the GPIO

1: Causes GPIO[7:0] to be held in reset by the soft

reset signal MSS_GPIO_7_0_SOFT_RESET

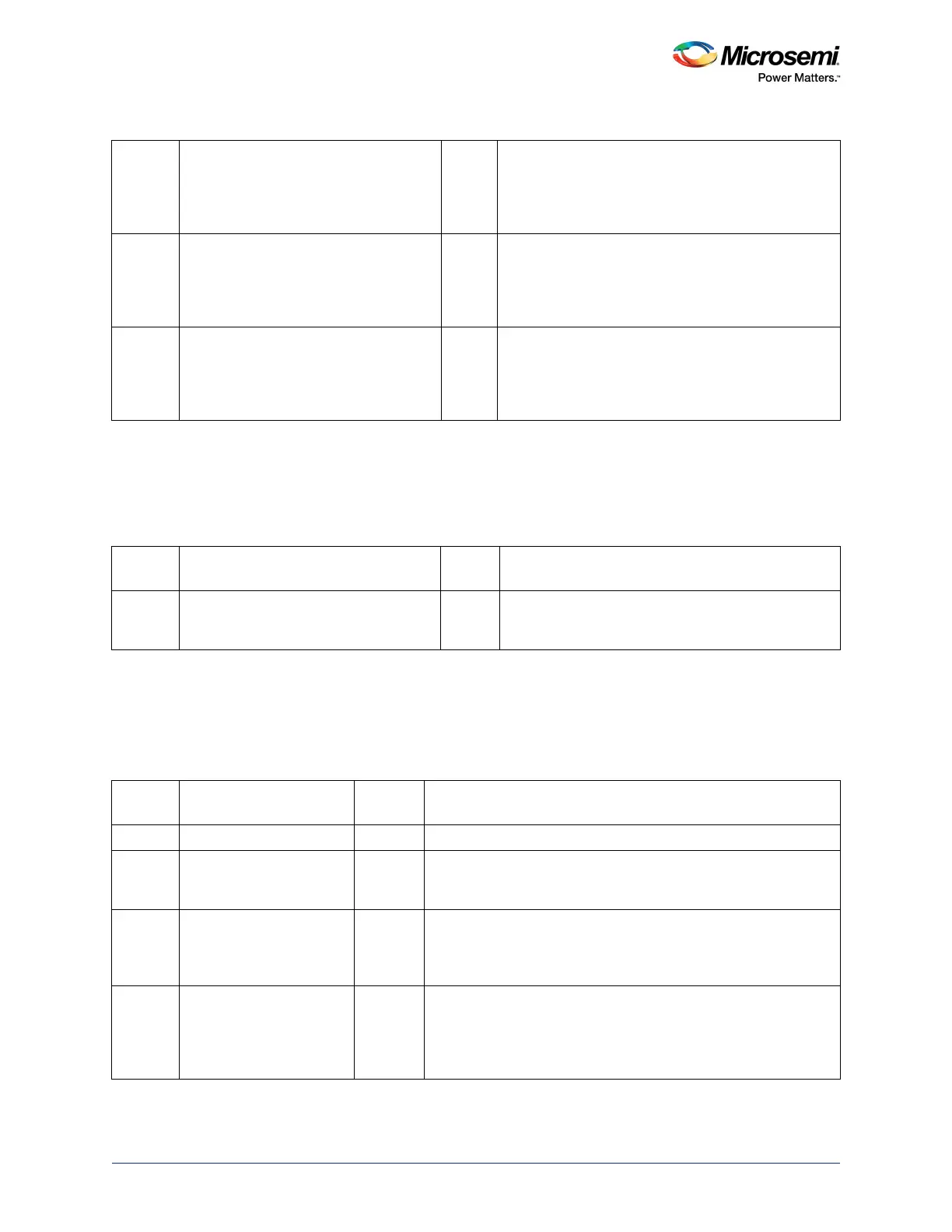

Table 679 • GPIN_SRC_SEL_CR

Bit

Number Name

Reset

Value Description

[31:0] MSS_GPINSOURCE 0 Used as select signal to generate a GPIO input signal

by selecting two output signals from different

IOMUXCELL or signals from I/O pads.

Table 680 • MDDR_CR

Bit

Number Name

Reset

Value Description

[31:4] Reserved 0

3 PHY_SELF_REF_EN 0 Indicates that the DRAM has been put into self-refresh. This is

used for automatic locking of the codes during intermediate runs

for DDRC. Not used in non-DDRIO modes.

2 F_AXI_AHB_MODE 0 Used by the SMC_FIC, DDR_FIC, and DDR CTL to select the

AXI/AHB interface in the fabric. Allowed values:

0: AHB interface is selected

1: AXI interface is selected

1 SDR_MODE 0 Used to select whether the MSS AXI interface accesses DDR

memory or SDR memory (or other memory types) inside the fabric.

Allowed values:

0: DDR memory is selected

1: SDR memory or other memory type is selected

Table 678 • GPIO_SYSRESET_SEL_CR (continued)

Loading...

Loading...