Watchdog Timer

UG0331 User Guide Revision 15.0 630

20.2 Functional Description

This following sub-sections provide a detailed description of the Watchdog timer.

20.2.1 Architecture Overview

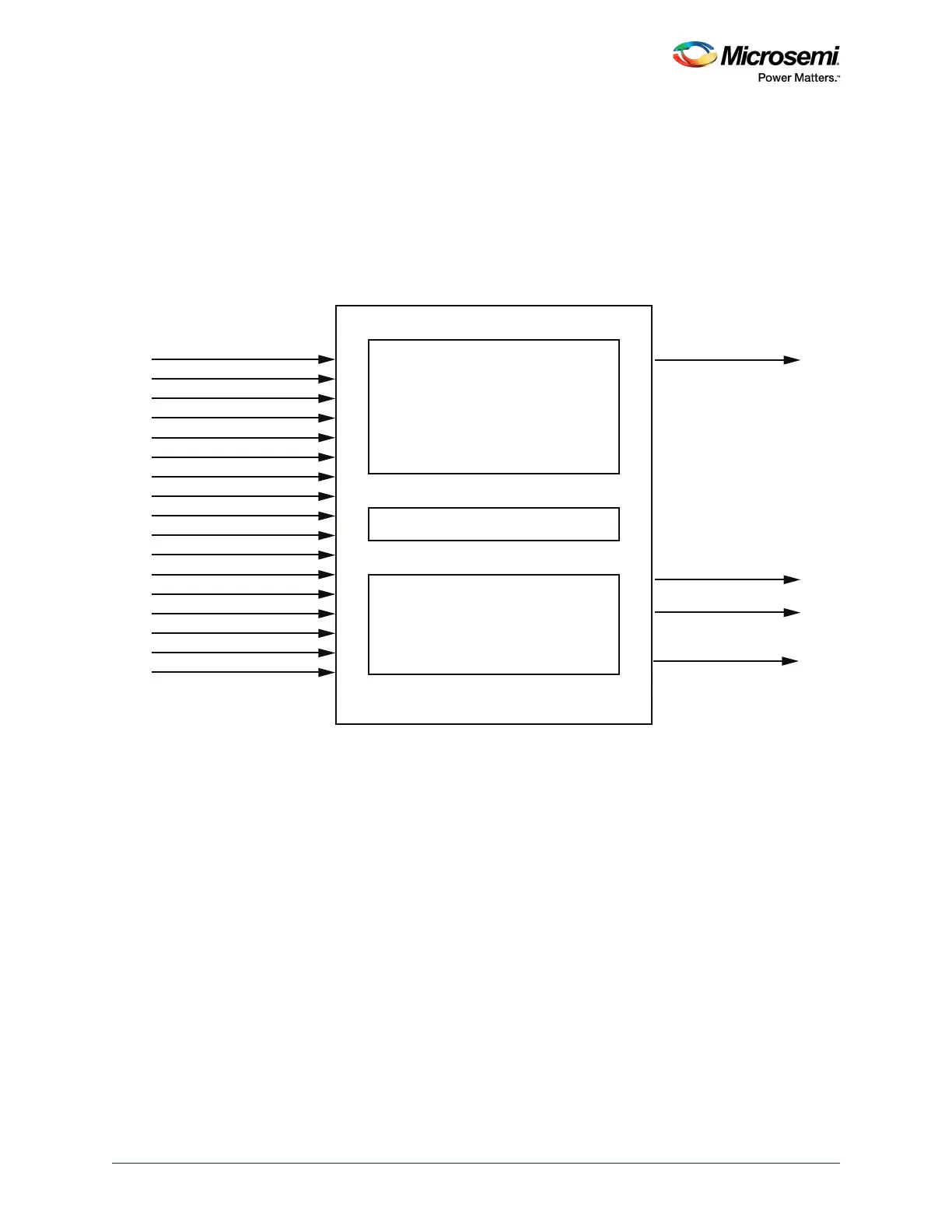

The watchdog timer consists of following components (as shown in the following figure):

• APB Interface

• 32-Bit Counter

• Timeout Detection

Figure 268 • Block Diagram for the Watchdog Timer

20.2.1.1 APB Interface

The watchdog timer has an APB interface through which the Cortex-M3 processor can access various

control and status registers to control and monitor its operation. The APB interface is clocked by the

PCLK0 clock signal. Any signals/values that cross between the RCOSCCLK and the PCLK clock

domains are synchronized with the watchdog timer.

20.2.1.2 32-Bit Counter

The operation of the watchdog timer is based on a 32-bit down counter that must be refreshed at regular

intervals by the Cortex-M3 processor. If not refreshed, the counter will time out. This either causes a

system reset or generates an interrupt to the processor, depending on the value of the WDOGMODE bit

as defined in the WDOG_CR Register.

The WDOG_CR register is one of the system registers that helps to configure the watchdog timer. In

normal operation, the generation of a reset or timeout interrupt by the watchdog timer does not occur

because the watchdog timer counter is refreshed on a regular basis.

When the device is powered up, the watchdog timer is enabled with the timeout period set to

approximately 10.47 seconds (if Vdd = 1.2 V). The WDOGENABLE bit in the WDOG_CR register

controls enabling/disabling of the watchdog timer.

PRDATA[31:0]

WDOGTIMEOUT

WDOGTIMEOUTINT

WDOGWAKEUPINT

APB Interface

Watchdog

32-Bit Counter

Timeout Detection

PCLK

PRESETn

PSEL

PWRITE

PENABLE

PADDR[7:0]

PWDATA[31:0]

PORESETN

RCOSCCLK

RCOSCRESETN

WDOGMODE

WDOGMVRP[31:0]

WDOGLOAD[25:0]

WDOGENABLE

SLEEPING

HALTED

PROGRAMMING

Loading...

Loading...