Cortex-M3 Processor (Reference Material)

UG0331 User Guide Revision 15.0 82

3.6.8.3.2 Operation

These instructions do the following:

1. Rotate the value from

Rm

right by 0, 8, 16 or 24 bits.

2. Extract bits from the resulting value:

•

SXTB

extracts bits [7:0] and sign extends to 32 bits.

•

UXTB

extracts bits [7:0] and zero extends to 32 bits.

•

SXTH

extracts bits [15:0] and sign extends to 32 bits.

•

UXTH

extracts bits [15:0] and zero extends to 32 bits.

3.6.8.3.3 Restrictions

Do not use SP and do not use PC.

3.6.8.3.4 Condition Flags

These instructions do not affect the flags.

Examples

SXTH R4, R6, ROR #16 ; Rotate R6 right by 16 bits, then obtain the lower

; halfword of the result and then sign extend to

; 32 bits and write the result to R4.

UXTB R3, R10 ; Extract lowest byte of the value in R10 and zero

; extend it, and write the result to R3.

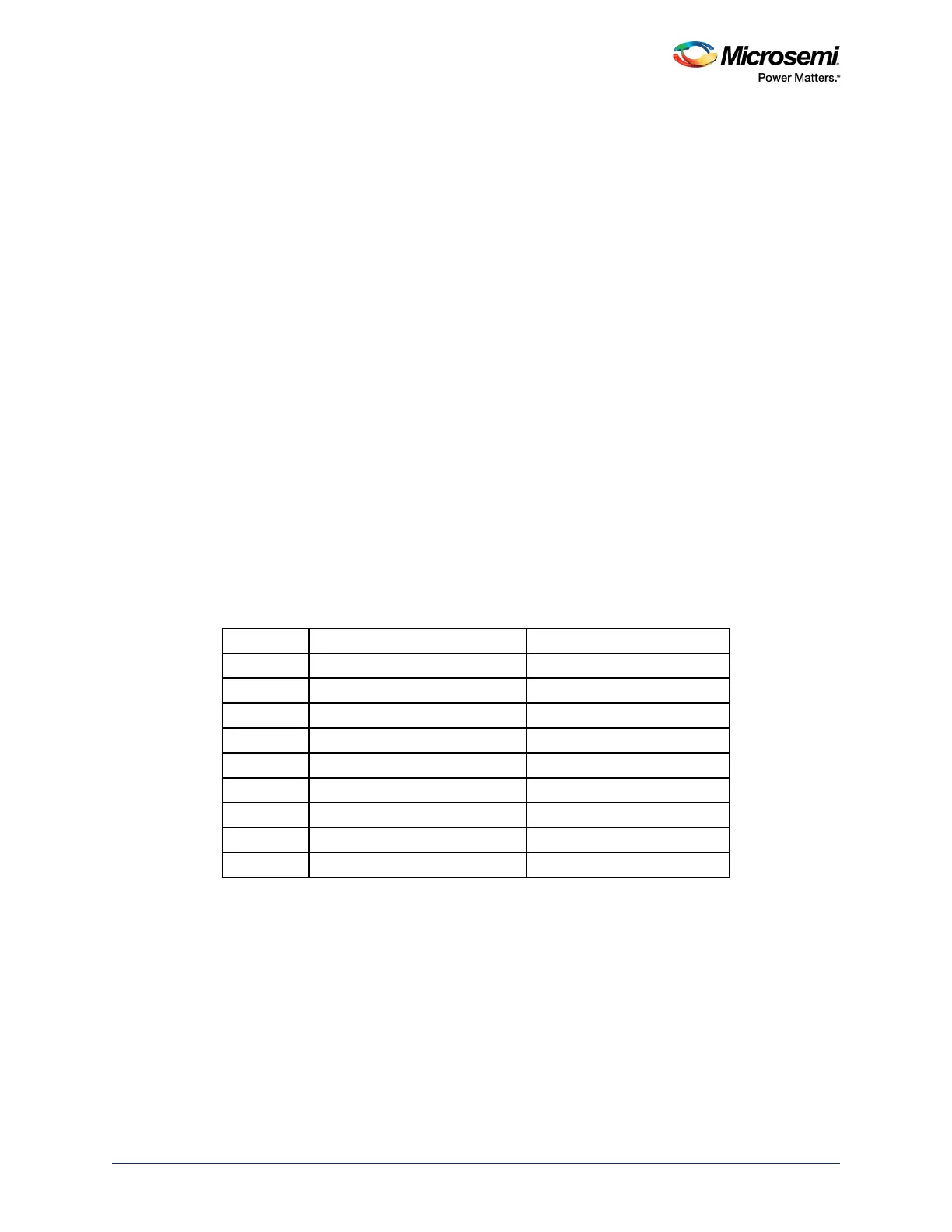

3.6.9 Branch and Control Instructions

The following table lists the branch and control instructions:

3.6.9.1 B, BL, BX, and BLX

Branch instructions.

3.6.9.1.1 Syntax

B{cond} label

BL{cond} label

BX{cond} Rm

BLX{cond} Rm

where:

B is branch (immediate).

Table 36 • Branch and Control Instructions

Mnemonic Brief description See

B Branch B, BL, BX, and BLX, page 83

BL Branch with Link B, BL, BX, and BLX, page 83

BLX Branch indirect with Link B, BL, BX, and BLX, page 83

BX Branch indirect B, BL, BX, and BLX, page 83

CBNZ Compare and Branch if Non Zero CBZ and CBNZ, page 85

CBZ Compare and Branch if Zero CBZ and CBNZ, page 85

IT If-Then IT, page 85

TBB Table Branch Byte TBB and TBH, page 87

TBH Table Branch Halfword TBB and TBH, page 87

Loading...

Loading...