MMUART Peripherals

UG0331 User Guide Revision 15.0 495

13.4.7 Interrupt Identification Register (IIR)

3 ELINBI R/W 0 Enables LIN break interrupt

0: Disabled (default)

1: Enabled

2 EPID_PEI R/W 0 Enables PID parity error interrupt

0: Disabled (default)

1: Enabled

1 ENACKI R/W 0 Enables NACK interrupt

0: Disabled (default)

1: Enabled

0 ERTOI R/W 0 Enables receiver timeout interrupt

0: Disabled (default)

1: Enabled

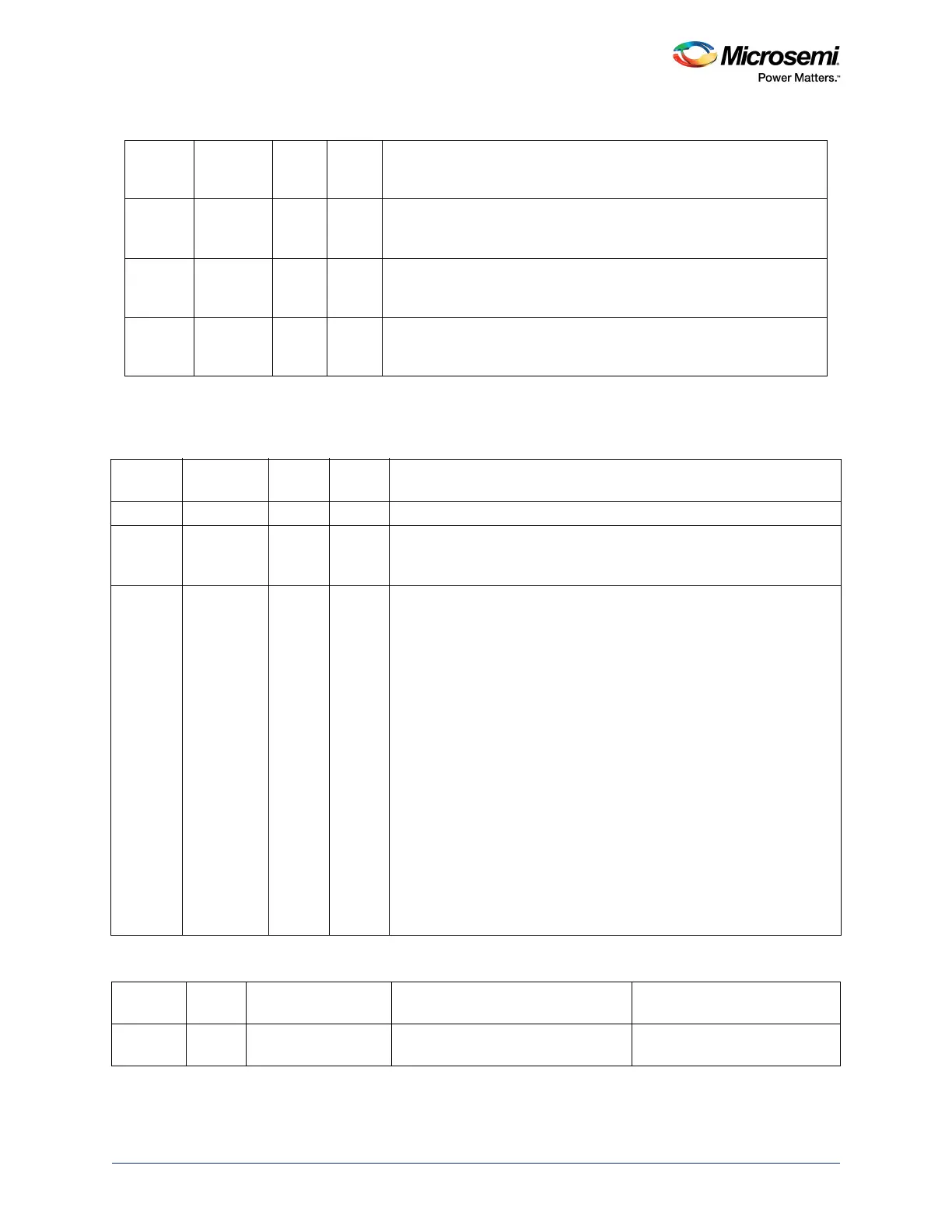

Table 477 • IIR

Bit

Number Name R/W

Reset

Value Description

[7:6] Mode R 0b11 Always 0b11. Enables FIFO mode.

[5:4] Reserved R 0 Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read- modify-write operation.

[3:0] IIR R 0b0001 Interrupt identification bits.

0b0110: Highest priority. Receiver line status interrupts due to overrun

error, parity error, framing error, or break interrupt. Reading the line

status register resets this interrupt.

0b0100: Second priority. Receive data available interrupt modem status

interrupt. Reading the receiver buffer register (RBR) or the FIFO drops

below the trigger level resets this interrupt.

0b1100: Second priority. Character timeout indication interrupt occurs

when no characters have been read from the Rx FIFO during the last

four character times and there was at least one character in it during this

time. Reading the RBR resets this interrupt.

0b0010: Third priority. Transmit holding register empty interrupt.

Reading the IIR or writing to the transmit holding register (THR) resets

the interrupt.

0b0000: Fourth priority. Modem status interrupt due to clear to send,

data set ready, ring indicator, or data carrier detect being asserted.

Reading the modem status register resets this interrupt.

0b0011: Fifth priority. Multi-mode interrupts can occur due to any of the

interrupts mentioned in IIM. For more details refer to Table 478,

page 495.

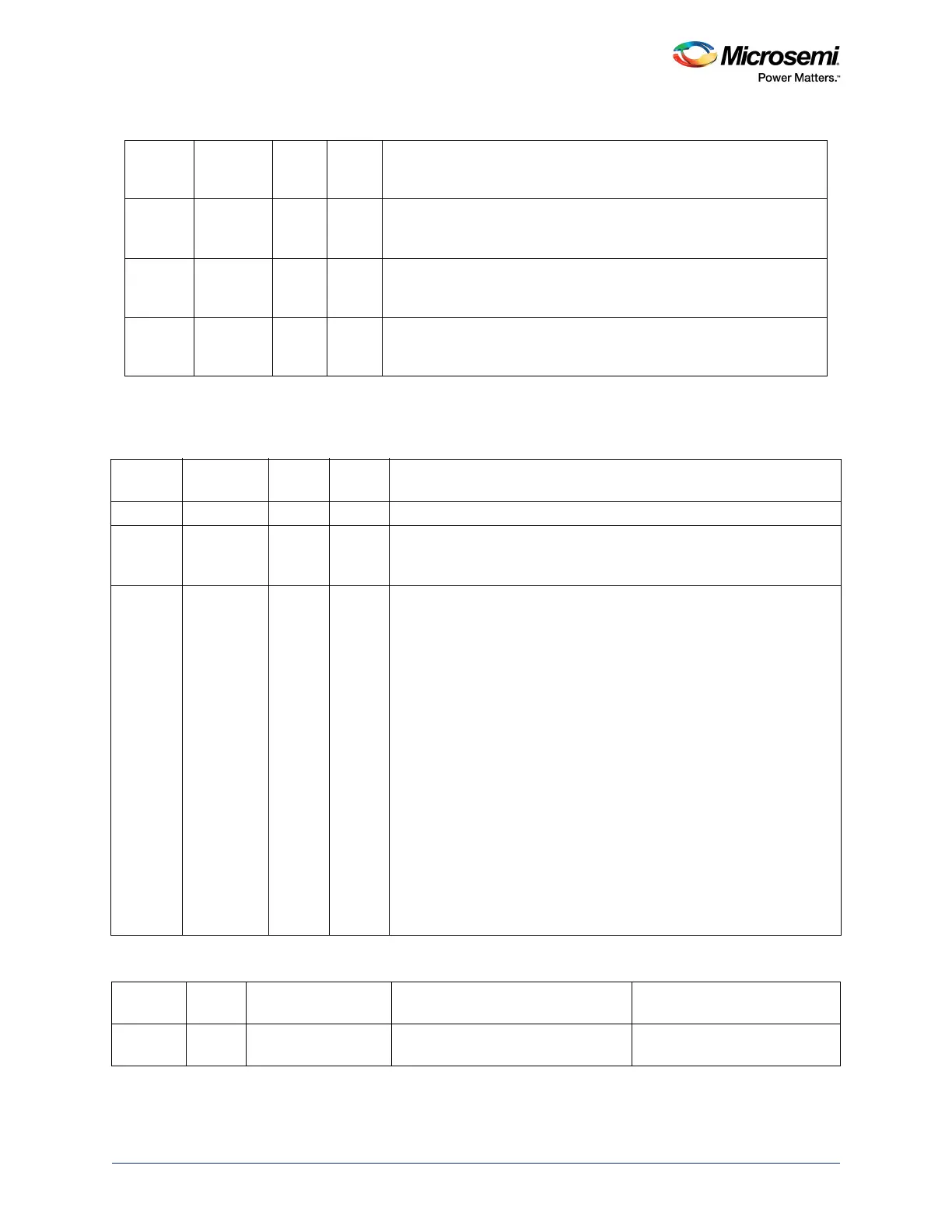

Table 478 • Interrupt Identification Bit Values

IIR

Value[3:0]

Priority

Level Interrupt Type Interrupt Source Interrupt Reset Control

0110 Highest Receiver line status Overrun error, parity error, framing

error, or break interrupt

Reading the line status register.

Table 476 • IEM (continued)

Loading...

Loading...