Universal Serial Bus OTG Controller

UG0331 User Guide Revision 15.0 344

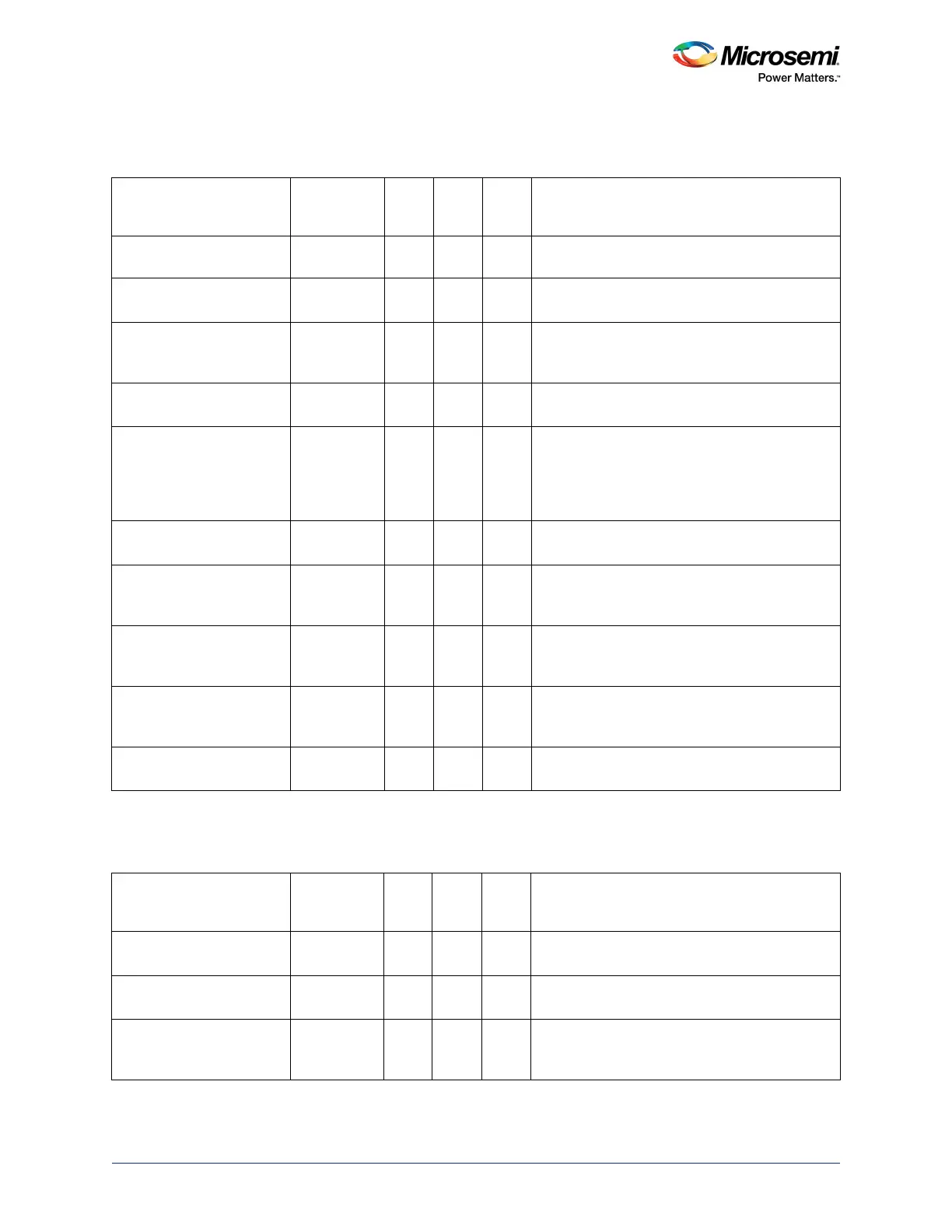

10.3.10.2 Endpoint1 Control and Status Registers

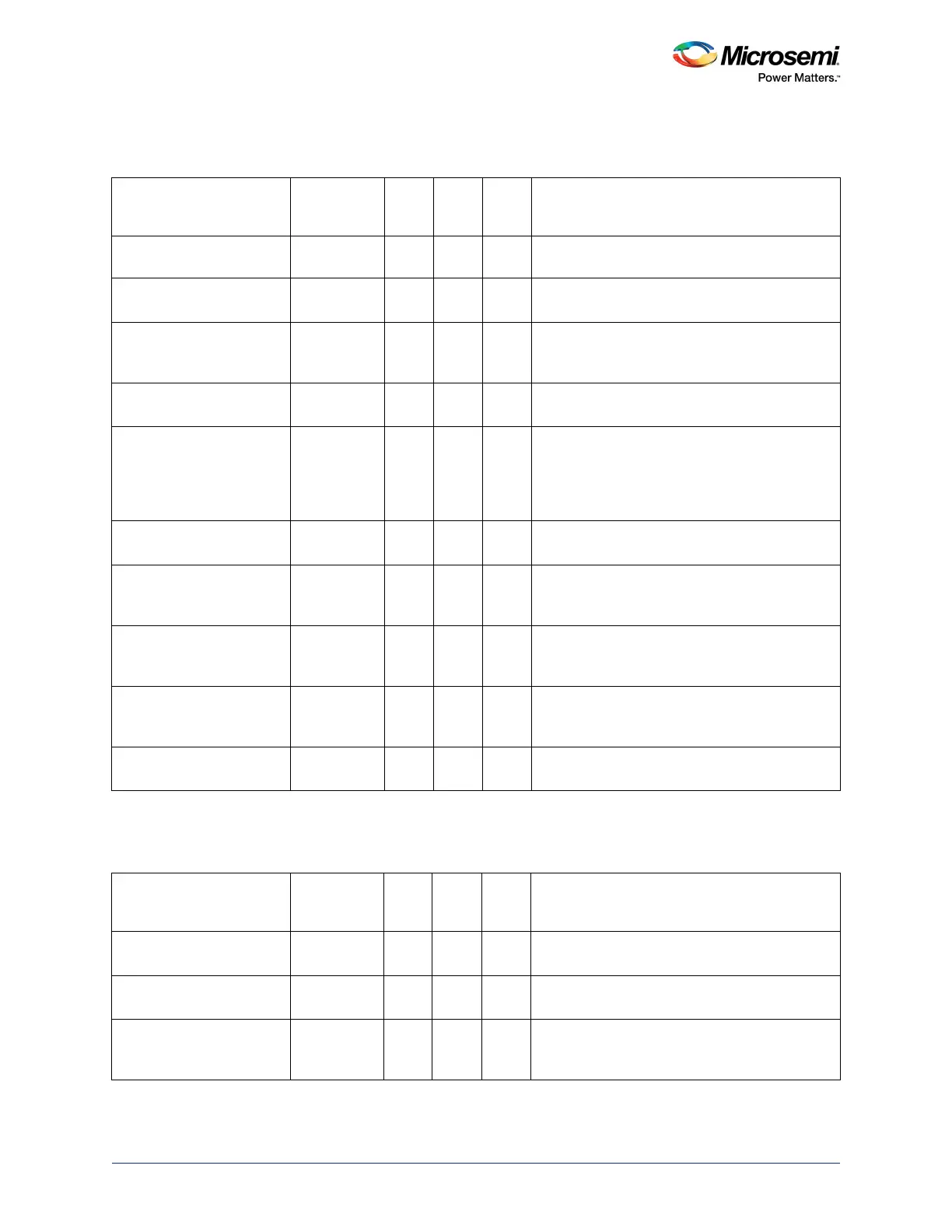

10.3.10.3 Endpoint2 Control and Status Registers

Table 272 • Endpoint1 Control and Status Registers

Register Name

Address

Offset from

0x40043000 Width

R/W

Type

Reset

Value Description

EP1_TX_MAX_P_REG 0x0110 16 R 0 Maximum packet size for host transmit

endpoint1.

EP1_TX_CSR_REG 0x0112 16 R 0 Provides control and status bits for transmit

endpoint1.

EP1_RX_MAX_P_REG 0x0114 16 RW 0 Defines the maximum amount of data that can be

transferred through receive endpoint1 in a single

operation.

EP1_RX_CSR_REG 0x0116 16 R 0 Provides control and status bits for transfers

through the receive endpoint1.

EP1_RX_COUNT_REG 0x0118 16 R 0 Holds the number of data bytes in the packet

currently in line to be read from the endpoint1

receive FIFO. If the packet is transmitted as

multiple bulk packets, the number given will be

for the combined packet.

EP1_TX_TYPE_REG 0x011A 8 W 0 Reads the number of bytes to be read from

peripheral endpoint1 transmit FIFO

EP1_TX_INTERVAL_REG 0x011B 8 RW 0 Sets the polling interval for interrupt/ISOC

transactions or the NAK response timeout on

bulk transactions for host transmit endpoint1.

EP1_RX_TYPE_REG 0x011C 8 RW 0 Sets the transaction protocol, speed, and

peripheral endpoint number for the host receive

endpoint1.

EP1_RX_INTERVAL_REG 0x011D 8 RW 0 Sets the polling interval for interrupt/ISOC

transactions or the NAK response timeout on

bulk transactions for host receive endpoint1.

EP1_FIFO_SIZE_REG 0x011E 8 R Returns the configured size of the endpoint1

receive FIFO and transmit FIFOs.

Table 273 • Endpoint2 Control and Status Registers

Register Name

Address

Offset from

0x40043000 Width

R/W

Type

Reset

Value Description

EP2_TX_MAX_P_REG 0x0120 16 RW 0 Maximum packet size for host transmit

endpoint2.

EP2_TX_CSR_REG 0x0122 16 R 0 Provides control and status bits for transmit

endpoint2.

EP2_RX_MAX_P_REG 0x0124 16 RW 0 Defines the maximum amount of data that can be

transferred through receive endpoint2 in a single

operation.

Loading...

Loading...