Embedded SRAM (eSRAM) Controllers

UG0331 User Guide Revision 15.0 190

ECC Checker and AHB Read Data Bus (HRDATA) Generator: In SECDED-ON mode, the ECC

Checker takes data (DO) from the memory as the input during the read or read-modify-write cycle and

checks for errors. One-bit errors detected are corrected.

If errors of more than one bit are detected, they are not corrected. In SECDED-OFF mode, the read out

data is directly given as output from this block. Error Status Signals are set if any errors are detected.

Error Status Signals: Error bits are inputs from the ECC Checker. If one error bit is High, it causes the

EDAC_1E signal to be High. In this case, there is no HRESP as the error is corrected. If there are two-bit

errors, it cause the EDAC_2E signal to be High. In this case, HRESP is set High because the error is not

corrected. The EDAC_1E and EDAC_2E signals are used to increment the ECC error counters within the

SYSREG block (and the failing address is also passed to the SYSREG block). When the HRESET to

ESRAMTOAHB is applied, it resets the EDAC address register which is maintained in ESRAMTOAHB

and it does not clear the contents of SRAM. EDAC error counters are maintained in System Register

which can be cleared either through same HRESET or by setting the CLR_EDAC_COUNTERS.

6.2.1 Memory Organization

The 40 KB of eSRAM memory is divided into two banks: 32 KB and 8 KB, to store 32 bits of data and 7

check bits in SECDED-ON mode. Physically, however, the memory is organized as

4096 × 40, which is 4096 × 5 bytes. When ECC is enabled, the fifth byte stores ECC values for the 32

bits of data. When ECC is disabled, the fifth byte location is used to create an additional 2 KB of user

memory. Four locations are used for each 32-bit word.

The following table shows the organization of 4096 × 40 bits in SECDED-ON mode. The total size of the

SRAM in the table is 40 KB. The locations show the memory used for the 32 KB block. ECC represents

the 7-bit ECC.

The following table shows the organization of 4096 × 40 bits in SECDED-OFF mode. The total size of the

SRAM in the table is 40 KB. The red locations show the memory used for the 32 KB block. The green

locations show memory used for the upper 8 KB block.

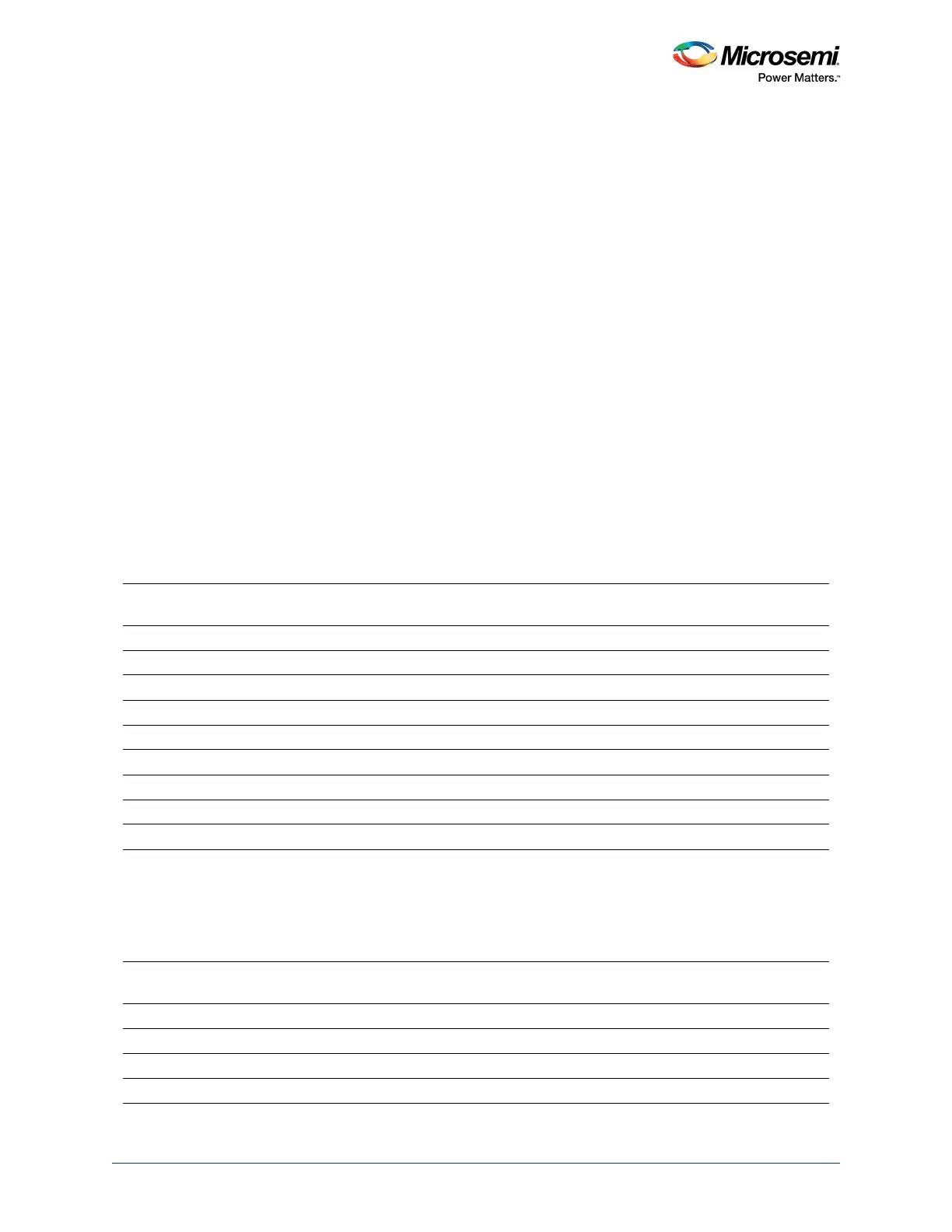

Table 119 • SRAM Organization in SECDED-ON Mode

RAM 4096X40_1

4096 x 40 Bits

RAM 4096X40_0

4096 x 40 Bits

Location Byte 4 Byte 3 Byte 2 Byte 1 Byte 0 Byte 4 Byte 3 Byte 2 Byte 1 Byte 0

0 ECC 4003 4002 4001 4000 ECC 0003 0002 0001 0000

1 ECC 4007 4006 4005 4004 ECC 0007 0006 0005 0004

2046 ECC 5FFB 5FFA 5FF9 5FF8 ECC 1FFB 1FFA 1FF9 1FF8

2047 ECC 5FFF 5FFE 5FFD 5FFC ECC 1FFF 1FFE 1FFD 1FFC

2048 ECC 6003 6002 6001 6000 ECC 2003 2002 2001 2000

2049 ECC 6007 6006 6005 6004 ECC 2007 2006 2005 2004

4094 ECC 7FFB 7FFA 7FF9 7FF8 ECC 3FFB 3FFA 3FF9 3FF8

4095 ECC 7FFF 7FFE 7FFD 7FFC ECC 3FFF 3FFE 3FFD 3FFC

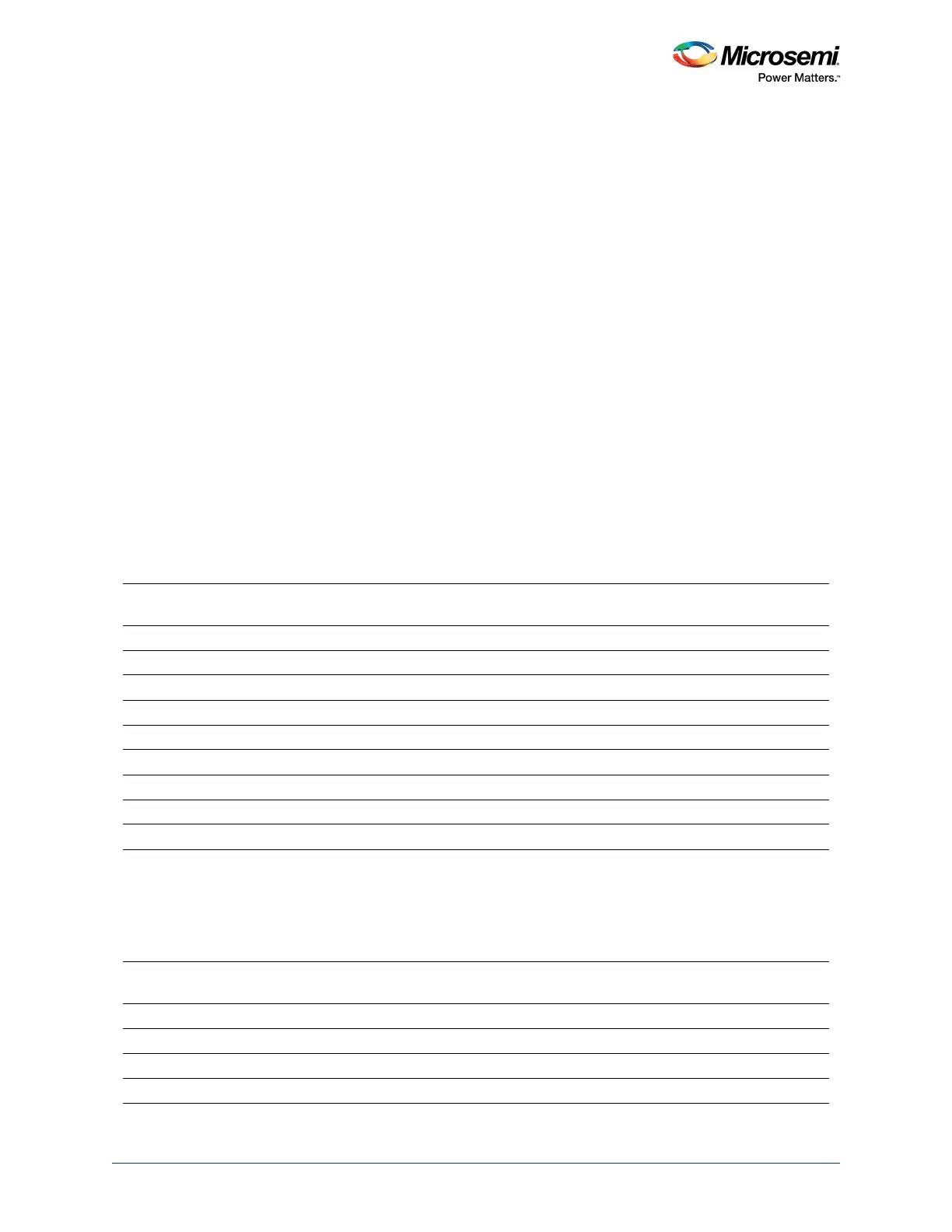

Table 120 • SRAM Organization in SECDED-OFF Mode

RAM 4096X40_1

4096 x 40 Bits

RAM 4096X40_0

4096 x 40 Bits

Location Byte 4 Byte 3 Byte 2 Byte 1 Byte 0 Byte 4 Byte 3 Byte 2 Byte 1 Byte 0

0 0001 4003 4002 4001 4000 0000 0003 0002 0001 0000

1 0005 4007 4006 4005 4004 0004 0007 0006 0005 0004

2046 1FF9 5FFB 5FFA 5FF9 5FF8 1FF8 1FFB 1FFA 1FF9 1FF8

Loading...

Loading...