Embedded SRAM (eSRAM) Controllers

UG0331 User Guide Revision 15.0 201

Note: Refer to Table 136, page 206 to clear the counter.

Note: Refer to Table 136, page 206 to clear the counter.

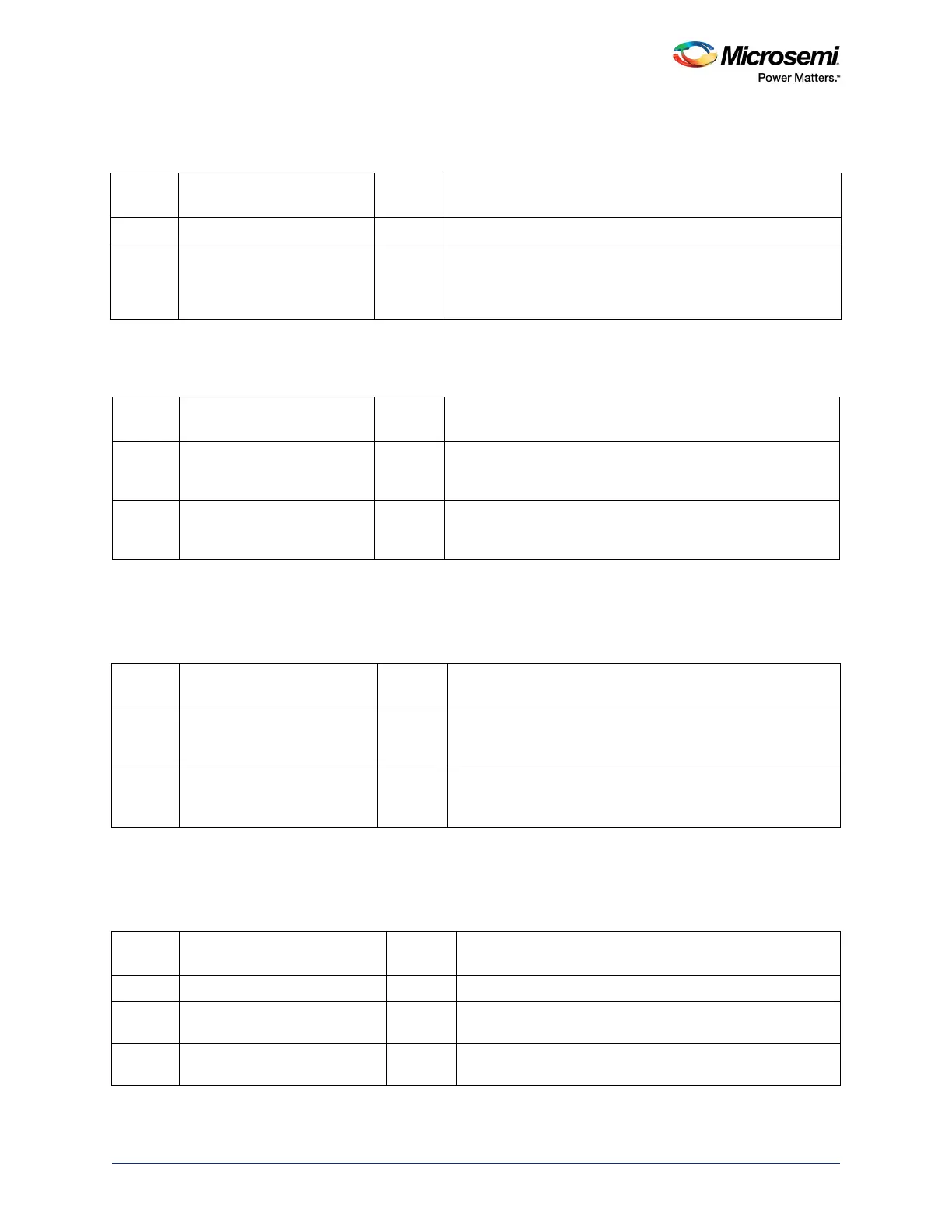

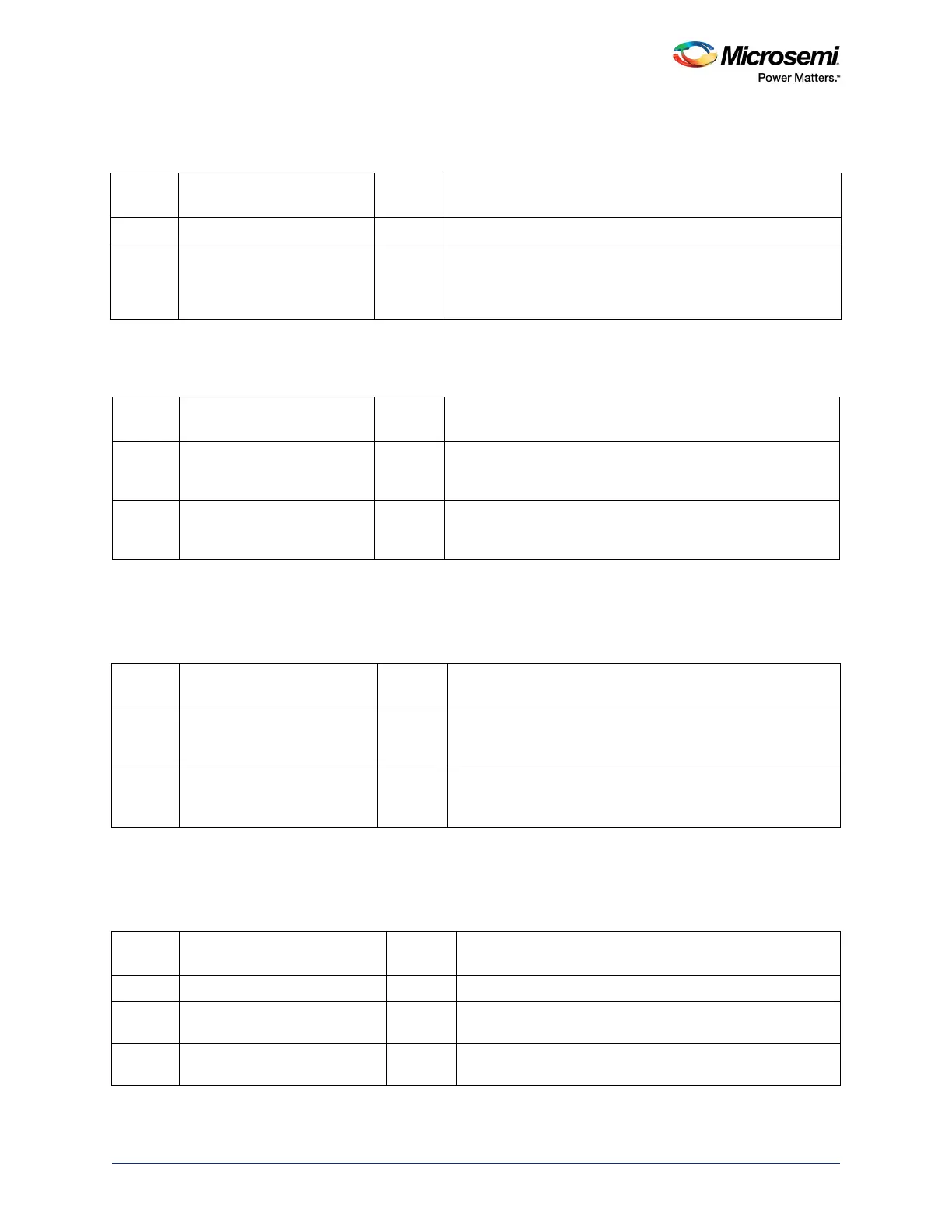

Table 126 • ESRAM_PIPELINE_CR

Bit

Number Name

Reset

Value Description

[31:1] Reserved 0 Reserved

0 ESRAM_PIPELINE_ENABLE 0x1 Controls the pipeline present in the read path of eSRAM

memory. Allowed values:

0: Pipeline will be bypassed.

1: Pipeline will be present in the memory read path.

Table 127 • ESRAM0_EDAC_CNT

Bit

Number Name

Reset

Value Description

[31:16] ESRAM0_EDAC_CNT_2E 0 16-bit counter that counts the number of 2-bit uncorrected

errors for eSRAM0. The counter will not roll back and will stay

at its maximum value.

[15:0] ESRAM0_EDAC_CNT_1E 0 16-bit counter that counts the number of 1-bit corrected errors

for eSRAM0. The counter will not roll back and will stay at its

maximum value.

Table 128 • ESRAM1_EDAC_CNT

Bit

Number Name

Reset

Value Description

[31:16] ESRAM1_EDAC_CNT_2E 0 16-bit counter that counts the number of 2-bit uncorrected

errors for eSRAM1. The counter will not roll back and will stay

at its maximum value.

[15:0] ESRAM1_EDAC_CNT_1E 0 16-bit counter that counts the number of 1-bit corrected errors

for eSRAM1. The counter will not roll back and will stay at its

maximum value.

Table 129 • ESRAM0_EDAC_ADR

Bit

Number Name

Reset

Value Description

[31:25] Reserved 0 Reserved

[25:13] ESRAM0_EDAC_2E_AD 0 Stores the address from eSRAM0 on which a 2-bit SECDED

error has occurred.

[12:0] ESRAM0_EDAC_1E_AD 0 Stores the address from eSRAM0 on which a 1-bit SECDED

error has occurred.

Loading...

Loading...