Ethernet MAC

UG0331 User Guide Revision 15.0 401

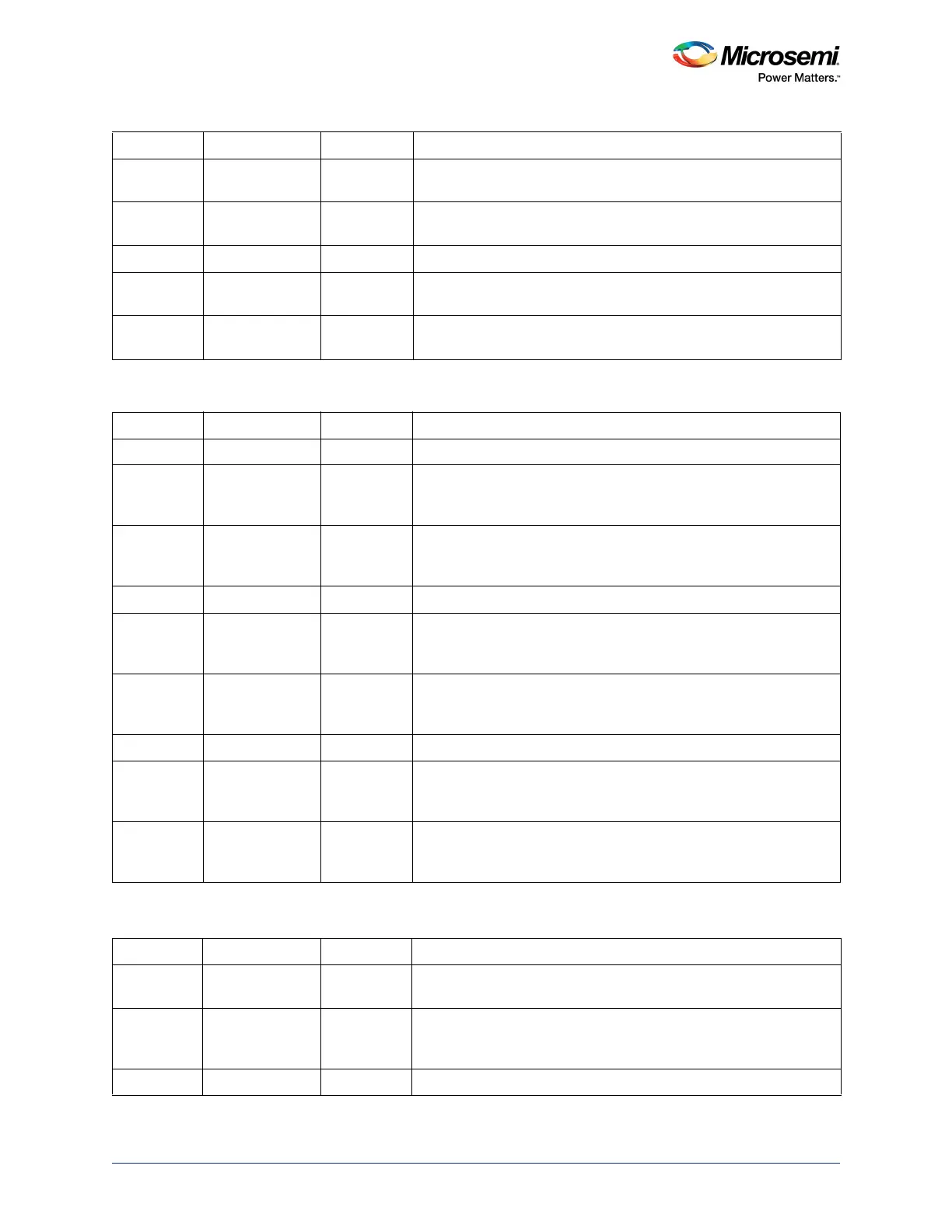

4 RxPktReceived

Mask

0x0 Setting this bit to ‘1’ enables the RxPktReceived bit in the

DMARxStatus register as an interrupt source.

3 Bus Error Mask 0x0 Setting this bit to ‘1’ enables the Bus Error bit in the DMATxStatus

register as an interrupt source.

2 Reserved 0x0 Reserved

1 Tx Underrun

Mask

0x0 Setting this bit to ‘1’ enables the TxUnderrun bit in the DMATxStatus

register as an interrupt source.

0 TxPktSent Mask 0x0 Setting this bit to ‘1’ enables the TxPktSent bit in the DMATxStatus

register as an interrupt source.

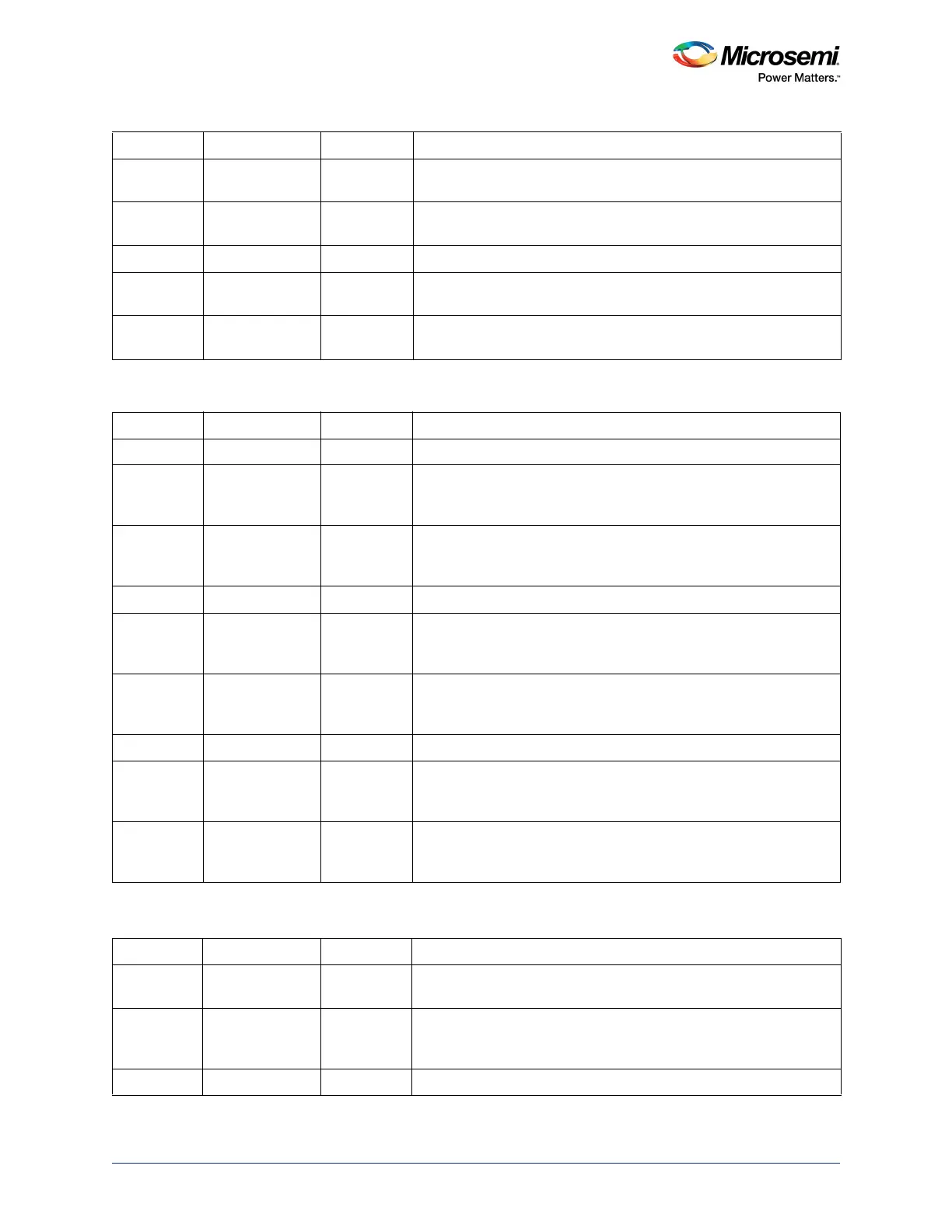

Table 346 • DMA_IRQ

Bit Number Name Reset Value Description

[31:8] Reserved 0x0 Reserved

7 Bus Error 0x0 This is set to ‘1’ to record a receive bus error interrupt when the Bus

Error bit in the DMARxStatus register and bit 7 of the DMAIntrMask

register are both set.

6 Rx Overflow 0x0 This is set to ‘1’ to record an Rx overflow interrupt when the

RxOverflow bit in the DMARxStatus register and bit 6 of the

DMAIntrMask register are both set.

5 Reserved 0x0 Reserved

4 RxPktReceived 0x0 This is set to ‘1’ to record a RxPktReceived interrupt when the

RxPktReceived bit in the DMARxStatus register and bit 4 of the

DMAIntrMask register are both set.

3 Bus Error 0x0 This is set to ‘1’ to record a transmit bus error interrupt when the

Bus Error bit in the DMATxStatus register and bit 3 of the

DMAIntrMask register are both set.

2 Reserved 0x0 Reserved

1 Tx Underrun 0x0 This is set to ‘1’ to record a Tx underrun interrupt when the

TxUnderrun bit in the DMATxStatus register and bit 1 of the

DMAIntrMask register are both set.

0 TxPktSent 0x0 This is set to ‘1’ to record a TxPktSent interrupt when the TxPktSent

bit in the DMATxStatus register and bit 0 of the DMAIntrMask

register are both set.

Table 347 • CFG1

Bit Number Name Reset Value Description

31 SOFT RESET 0x1 Setting this bit will put all modules within the PE-MCXMAC in the

reset except the Host Interface.

30 SIMULATION

RESET

0x0 Setting this bit will reset those registers, such as the random backoff

timer, which are not controlled by the normal resets. (simulation

only)

[29:20] Reserved 0x0 Reserved

Table 345 • DMA_IRQ_MASK (continued)

Bit Number Name Reset Value Description

Loading...

Loading...