Cortex-M3 Processor (Reference Material)

UG0331 User Guide Revision 15.0 48

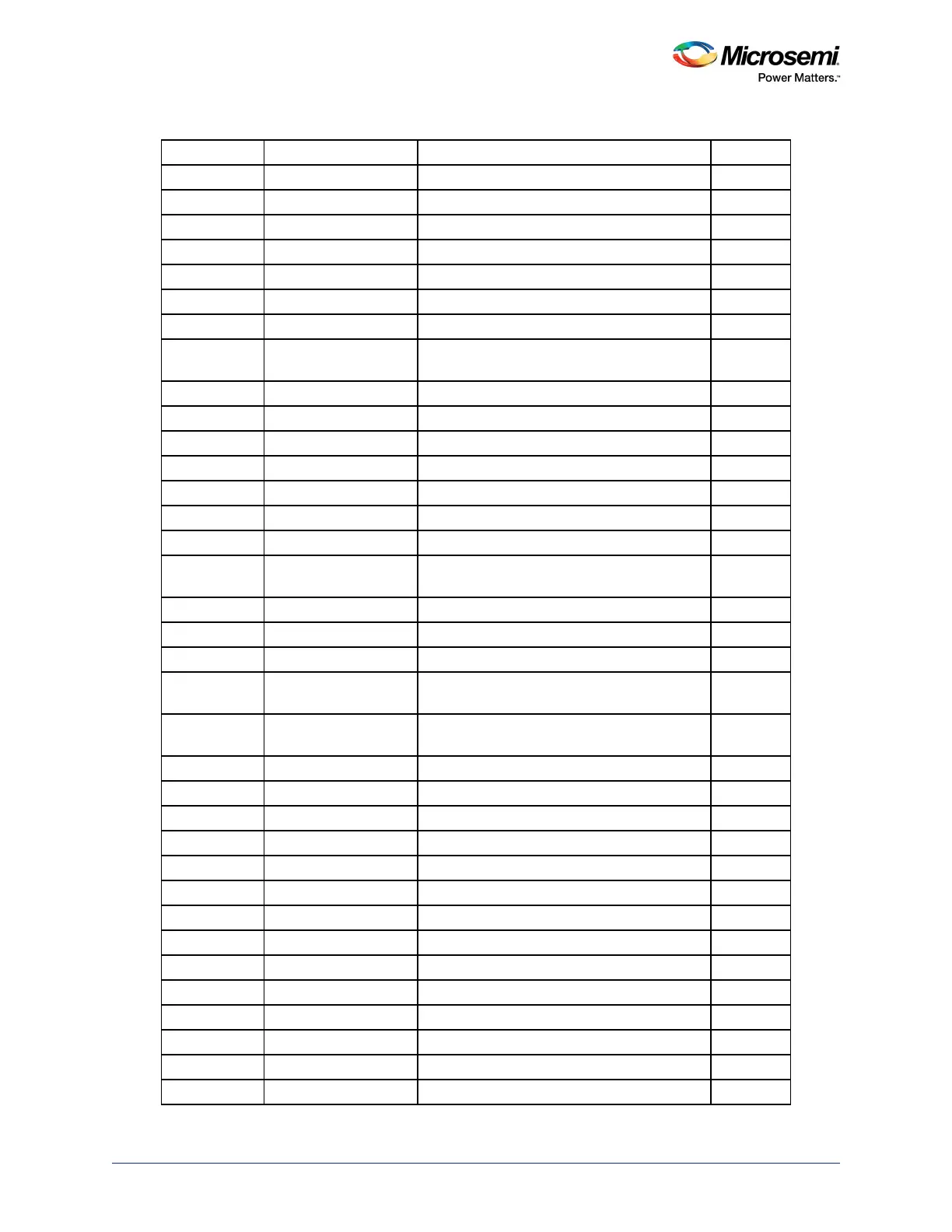

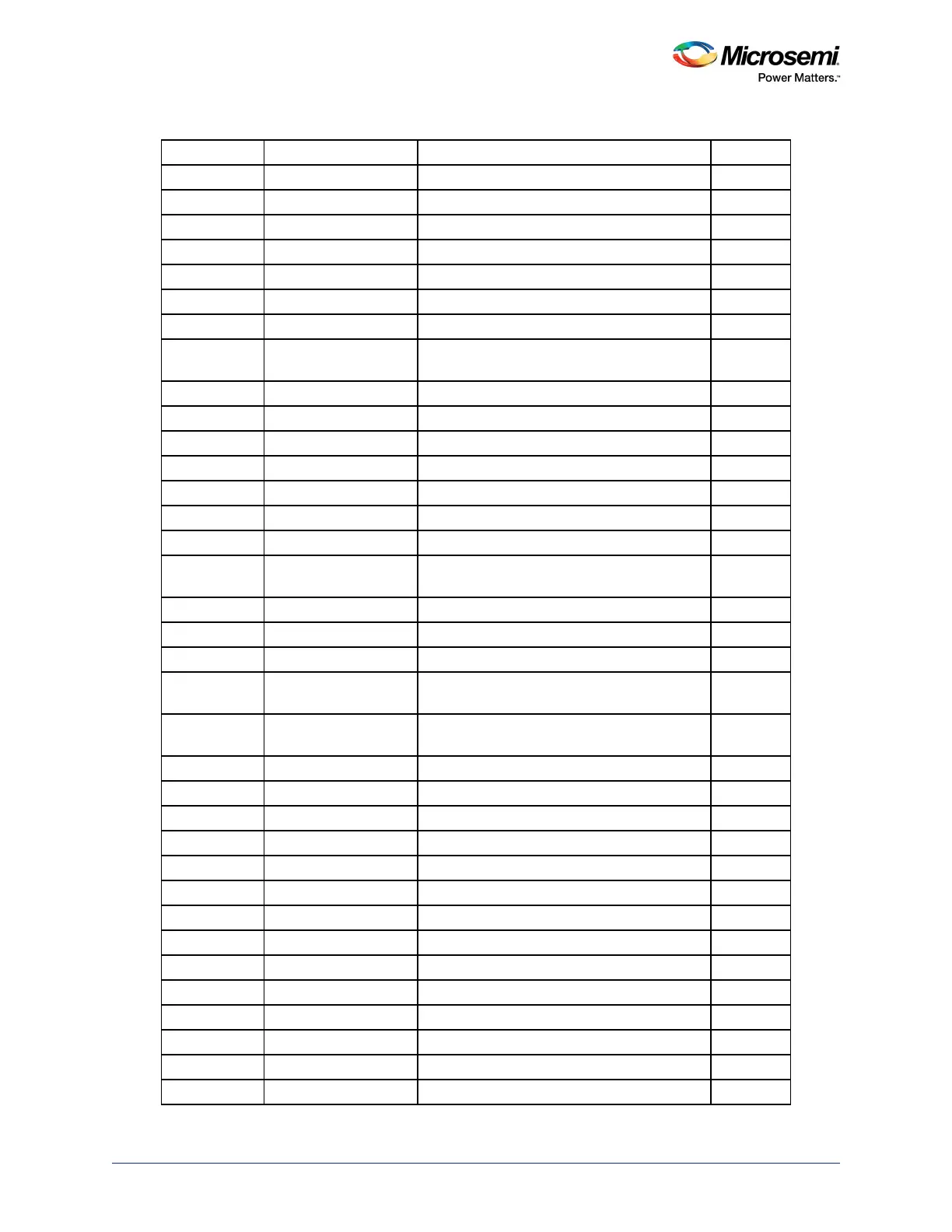

ORN, ORNS {Rd,} Rn, Op2 Logical OR NOT N, Z, C

ORR, ORRS {Rd,} Rn, Op2 Logical OR N, Z, C

POP reglist Pop registers from stack

PUSH reglist Push registers onto stack

RBIT Rd, Rn Reverse Bits

REV Rd, Rn Reverse byte order in a word

REV16 Rd, Rn Reverse byte order in each halfword

REVSH Rd, Rn Reverse byte order in bottom halfword and

sign extend

ROR, RORS Rd, Rm, <Rs|#n> Rotate Right N, Z, C

RRX, RRXS Rd, Rm Rotate Right with Extend N, Z, C

RSB, RSBS {Rd,} Rn, Op2 Reverse Subtract N, Z, C, V

SBC, SBCS {Rd,} Rn, Op2 Subtract with Carry N, Z, C, V

SBFX Rd, Rn, #lsb, #width Signed Bit Field Extract

SDIV {Rd,} Rn, Rm Signed Divide

SEV Send Event

SMLAL RdLo, RdHi, Rn, Rm Signed Multiply with Accumulate (32 x 32 +

64), 64-bit result

SMULL RdLo, RdHi, Rn, Rm Signed Multiply (32 x 32), 64-bit result

SSAT Rd, #n, Rm {,shift #s} Signed Saturate Q

STM Rn{!}, reglist Store Multiple registers, increment after

STMDB,

STMEA

Rn{!}, reglist Store Multiple registers, decrement before

STMFD,

STMIA

Rn{!}, reglist Store Multiple registers, increment after

STR Rt, [Rn, #offset] Store Register word

STRB, STRBT Rt, [Rn, #offset] Store Register byte

STRD Rt, Rt2, [Rn, #offset] Store Register two words

STREX Rd, Rt, [Rn, #offset] Store Register Exclusive

STREXB Rd, Rt, [Rn] Store Register Exclusive Byte

STREXH Rd, Rt, [Rn] Store Register Exclusive Halfword

STRH, STRHT Rt, [Rn, #offset] Store Register Halfword

STRT Rt, [Rn, #offset] Store Register word

SUB, SUBS {Rd,} Rn, Op2 Subtract N, Z, C, V

SUB, SUBW {Rd,} Rn, #imm12 Subtract N, Z, C, V

SVC #imm Supervisor Call

SXTB {Rd,} Rm {,ROR #n} Sign extend a byte

SXTH {Rd,} Rm {,ROR #n} Sign extend a halfword

TBB [Rn, Rm] Table Branch Byte

Table 26 • Cortex-M3 Processor Instructions (continued)

Mnemonic Operands Brief description Flags

Loading...

Loading...