Ethernet MAC

UG0331 User Guide Revision 15.0 394

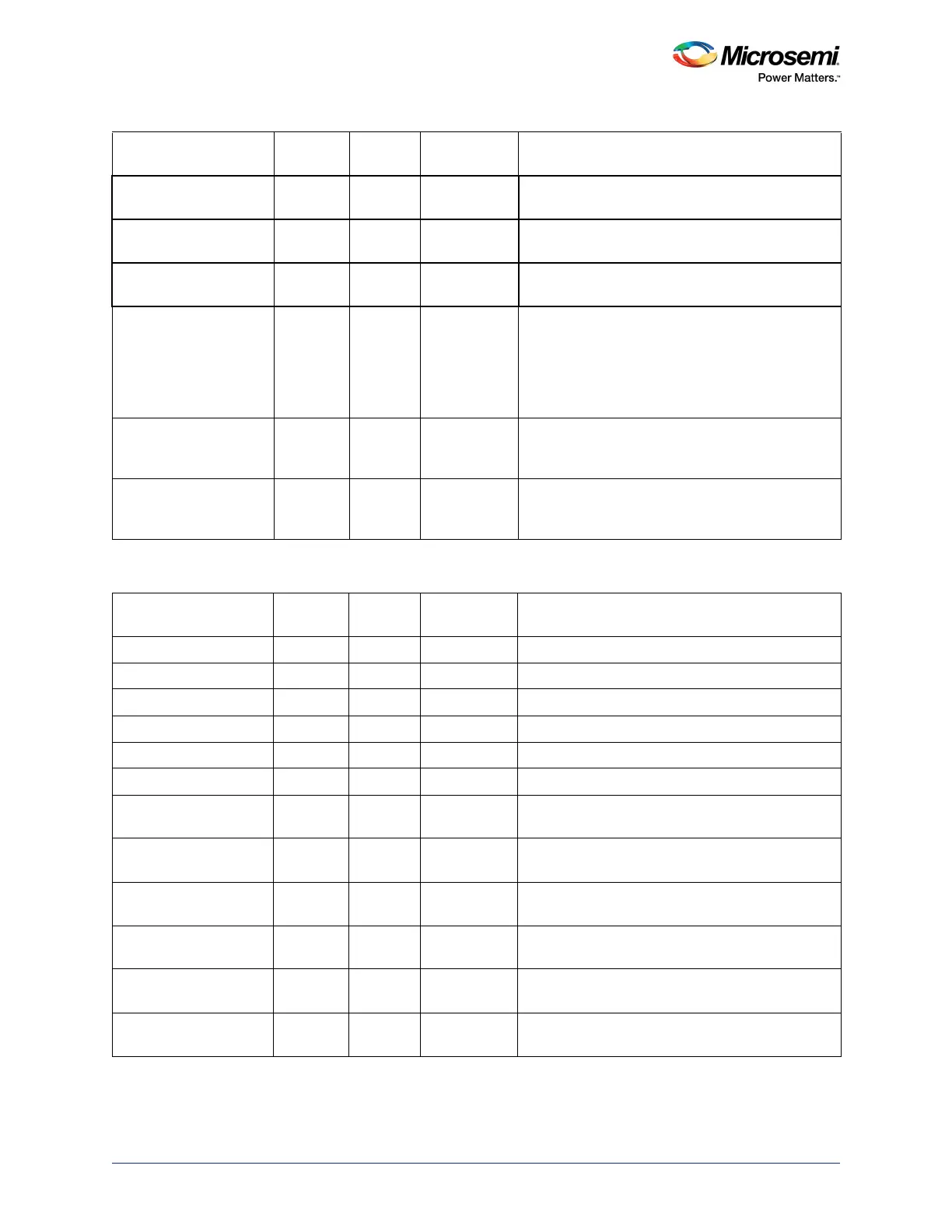

MII_STATUS 0x30 RO 0x0 Following an MII Mgmt read cycle, the 16-bit data

can be read from this location.

MII_INDICATORS 0x34 RO 0x0 This indicates MII management block is currently

performing an MII Mgmt read or write cycle.

INTERFACE_CTRL 0x38 R/W 0x0 This configures PERMII for 10 Mbps or 100 Mbps

speed.

INTERFACE_STATUS 0x3C RO 0x0 This indicates the serial MII PHY has detected a

jabber condition on the link.

This also indicates the serial MII PHY has detected

a valid link.

This indicates the serial MII PHY is operating in

Full-duplex mode.

STATION_ADDRESS1 0x40 R/W 0x0 The register fields hold the station address. Station

address is the 48-bit programmed receive frame’s

destination address.

STATION_ADDRESS2 0x44 R/W 0x0 The register fields hold the station address. The

station address is the 48-bit programmed receive

frame’s destination address.

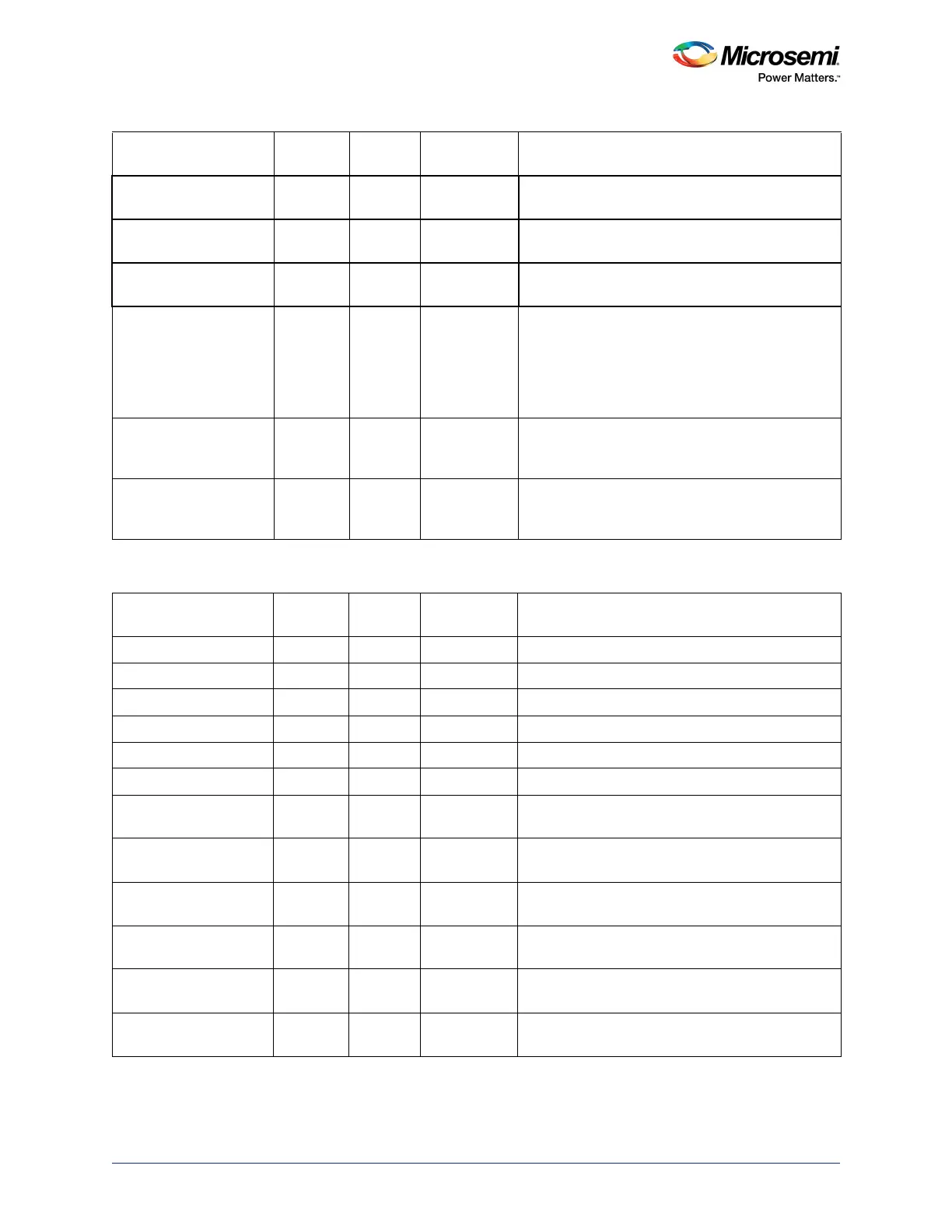

Table 334 • EMAC A-MCXFIFO Register Map

Register Name

Address

Offset

Register

Type Reset Value Description

FIFO_CFG0 0x48 R/W 0x0 Definition of A-MCXFIFO configuration register 0

FIFO_CFG1 0x4C R/W 0x0FFFFFFF Definition of A-MCXFIFO configuration register 1

FIFO_CFG2 0x50 R/W 0x1FFF1FFF Definition of A-MCXFIFO configuration register 2

FIFO_CFG3 0x54 R/W 0xFFF0FFF Definition of A-MCXFIFO configuration register 3

FIFO_CFG4 0x58 R/W 0x0 Definition of A-MCXFIFO configuration register 4

FIFO_CFG5 0x5C R/W 0x3FFFF Definition of A-MCXFIFO configuration register 5

FIFO_RAM_ACCESS0 0x60 R/W 0x0 The FIFO RAM access register 0 is intended for

non-real-time RAM testing and debug.

FIFO_RAM_ACCESS1 0x64 R/W 0x0 The FIFO RAM access register 1 is intended for

non-real-time RAM testing and debug.

FIFO_RAM_ACCESS2 0x68 R/W 0x0 The FIFO RAM access register 2 is intended for

non-real-time RAM testing and debug.

FIFO_RAM_ACCESS3 0x6C RO 0x0 The FIFO RAM access register 3 is intended for

non-real-time RAM testing and debug.

FIFO_RAM_ACCESS4 0x70 R/W 0x0 The FIFO RAM access register 4 is intended for

non-real-time RAM testing and debug.

FIFO_RAM_ACCESS5 0x74 R/W 0x0 The FIFO RAM access register 5 is intended for

non-real-time RAM testing and debug.

Table 333 • EMAC PE-MCXMAC Register Map (continued)

Register Name

Address

Offset

Register

Type Reset Value Description

Loading...

Loading...