MSS GPIO

UG0331 User Guide Revision 15.0 574

16.3.2.2 Use Model 2: GPIO Loopback Mode

GPIO Loopback mode (shown in the following figure) is looping back all the 32 GPIOs by controlling the

MSS_LOOPBACK bit of LOOPBACK_CR System register.

1. Enable GPIOs using MSS configurator in Libero SoC.

2. Initialize all 32 GPIOs to a predefined state using the MSS_GPIO_init API in SoftConsole or Libero

SoC.

3. Set the MSS_GPIOLOOPBACK1 bit of the LOOPBACK_CR System register in the SoftConsole

application.

4. Configure GPIOs as output and input by using the MSS_GPIO_config API.

5. Use the MSS_GPIO_set_output API to set the value of the GPIO_OUT register.

6. Use the interrupt API MSS_GPIO_enable_irq to configure all 32 GPIO outputs as an interrupts to the

Cortex-M3 processor.

(or)

Use the API MSS_GPIO_get_inputs to read the looped back values and use them the application.

Figure 249 • GPIO Loopback Diagram

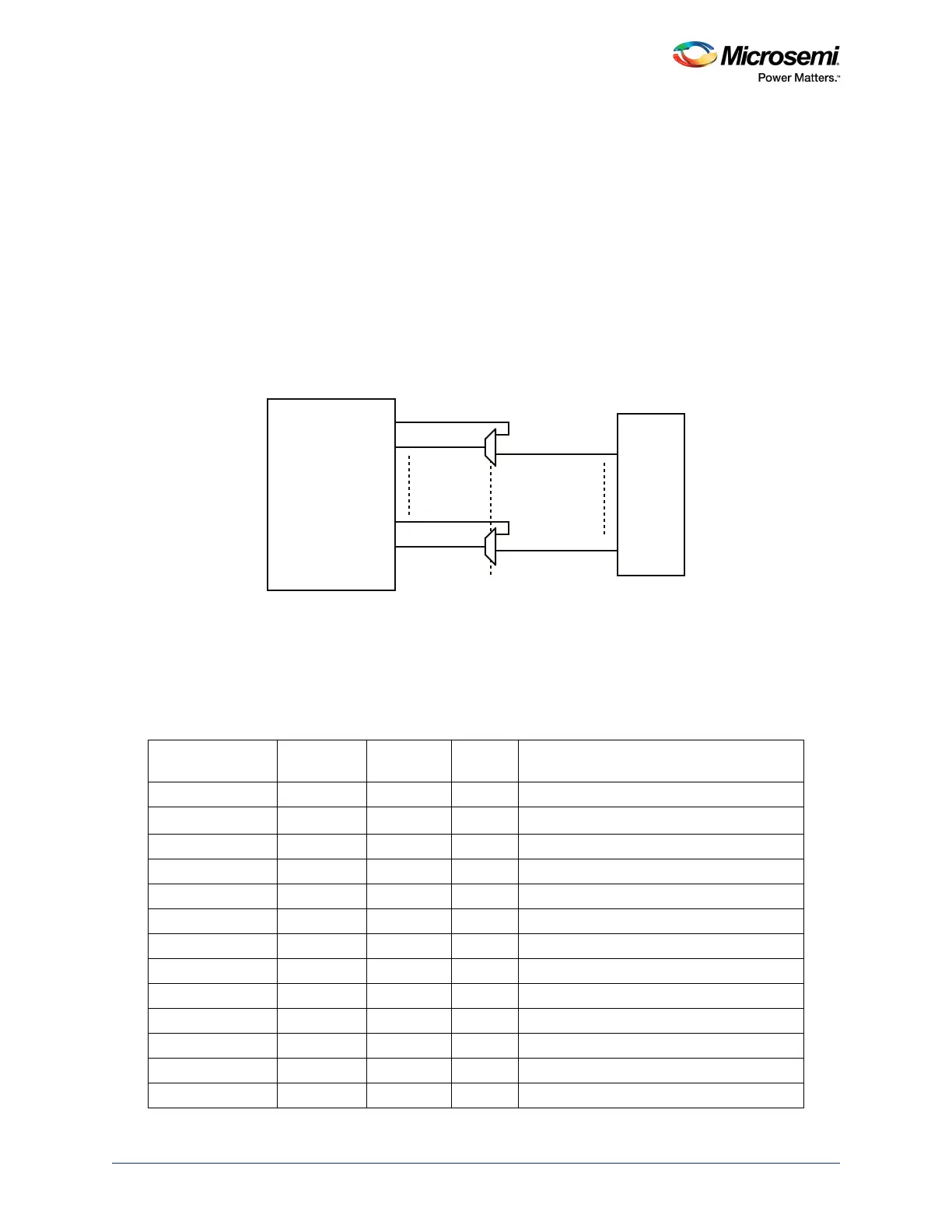

16.4 GPIO Register Map

The base address of the MSS GPIO block is 0x40013000.The address offset of each MSS GPIO register

is provided in the following table. The table also includes configuration, input, and output registers.

Table 538 • MSS GPIO Register Map

Register Name

Address

Offset

Register

Type

Reset

Value Description

GPIO_0_CFG 0x00 R/W 0x0 Configuration register for GPIO 0

GPIO_1_CFG 0x04 R/W 0x0 Configuration register for GPIO 1

GPIO_2_CFG 0x08 R/W 0x0 Configuration register for GPIO 2

GPIO_3_CFG 0x0C R/W 0x0 Configuration register for GPIO 3

GPIO_4_CFG 0x10 R/W 0x0 Configuration register for GPIO 4

GPIO_5_CFG 0x14 R/W 0x0 Configuration register for GPIO 5

GPIO_6_CFG 0x18 R/W 0x0 Configuration register for GPIO 6

GPIO_7_CFG 0x1C R/W 0x0 Configuration register for GPIO 7

GPIO_8_CFG 0x20 R/W 0x0 Configuration register for GPIO 8

GPIO_9_CFG 0x24 R/W 0x0 Configuration register for GPIO 9

GPIO_10_CFG 0x28 R/W 0x0 Configuration register for GPIO 10

GPIO_11_CFG 0x2C R/W 0x0 Configuration register for GPIO 11

GPIO_12_CFG 0x30 R/W 0x0 Configuration register for GPIO 12

GPIO_0_OUT

GPIO_31_OUT

GPIO_0_IN

MSS_GPIOLOOPBACK

(bit3 of LOOPBACK_CR system register)

GPIO_31_IN

GPIO

IOMUX

Loading...

Loading...