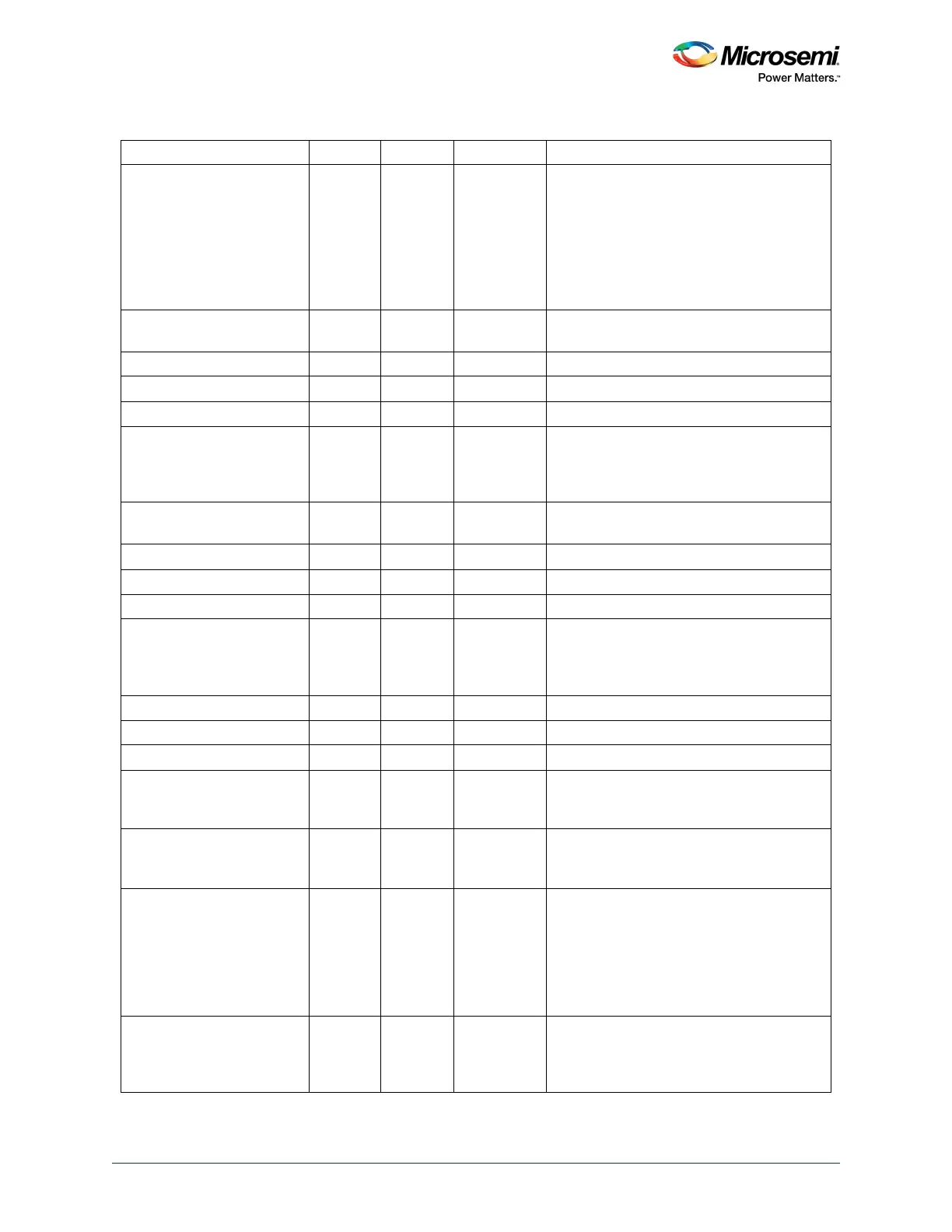

CAN Controller

UG0331 User Guide Revision 15.0 453

CAN_COMMAND 0x014 R/W 0 The CAN controller can be used in different

operating modes. By disabling transmitting

data, it is possible to use the CAN in

Listen-only mode, enabling features such as

automatic bit rate detection. Before starting

the CAN controller, all the CAN configuration

registers have to be set according to the

target application.

TX_MSG0_CTRL_CMD 0x020 R/W 0 Transmit Message0 buffer control and

command register

TX_MSG0_ID 0x024 R/W 0 Transmit Message0 buffer identifier register

TX_MSG0_DATA_HIGH 0x028 R/W 0 Transmit Message0 buffer data high register

TX_MSG0_DATA_LOW 0x02C R/W 0 Transmit Message0 buffer data low register

TX_BUF_STATUS 0x0C R 0 Transmit (TX) message buffer status.

This bundles transmit request (TxReq)

pending flags from all 32 receive message

buffers.

RX_MSG0_CTRL_CMD 0x220 R/W 0 Receive Message0 buffer command and

control register

RX_MSG0_ID 0x224 R/W 0 Receive Message0 buffer Identifier register

RX_MSG0_DATA_HIGH 0x228 R/W 0 Receive Message0 buffer data high register

RX_MSG0_DATA_LOW 0x22C R/W 0 Receive Message0 buffer data low register

RX_MSG0_AMR 0x230 R/W 0 Acceptance mask register (AMR)

The AMR register defines whether the

incoming bit is checked against the ACR

register

RX_MSG0_ACR 0x234 R/W 0 Acceptance code register (ACR)

RX_MSG0_AMR_DATA 0x238 R/W 0 AMR- Data

RX_MSG0_ACR_DATA 0x23C R/W 0 ACR- Data

RX_BUF_STATUS 0x08 R 0 Receive (RX) message buffer status. This

bundles message available (MsgAv) flags

from all 32 receive message buffers.

ECR 0x01C RW 0 Error capture register

Can be used to perform additional CAN bus

diagnostics

ERROR_STATUS 0x010 R 0 CAN error status indicator register

Provides visibility into CAN controller error

state, receive error count, and transmit error

count. Special flags to report error counter

values equal to or in excess of 96 errors are

available to indicate heavily disturbed bus

situations.

INT_ENABLE 0x004 R/W 0 Interrupt enable register

Writing 1 to a particular bit enables the

corresponding interrupt source as set in

INT_STATUS.

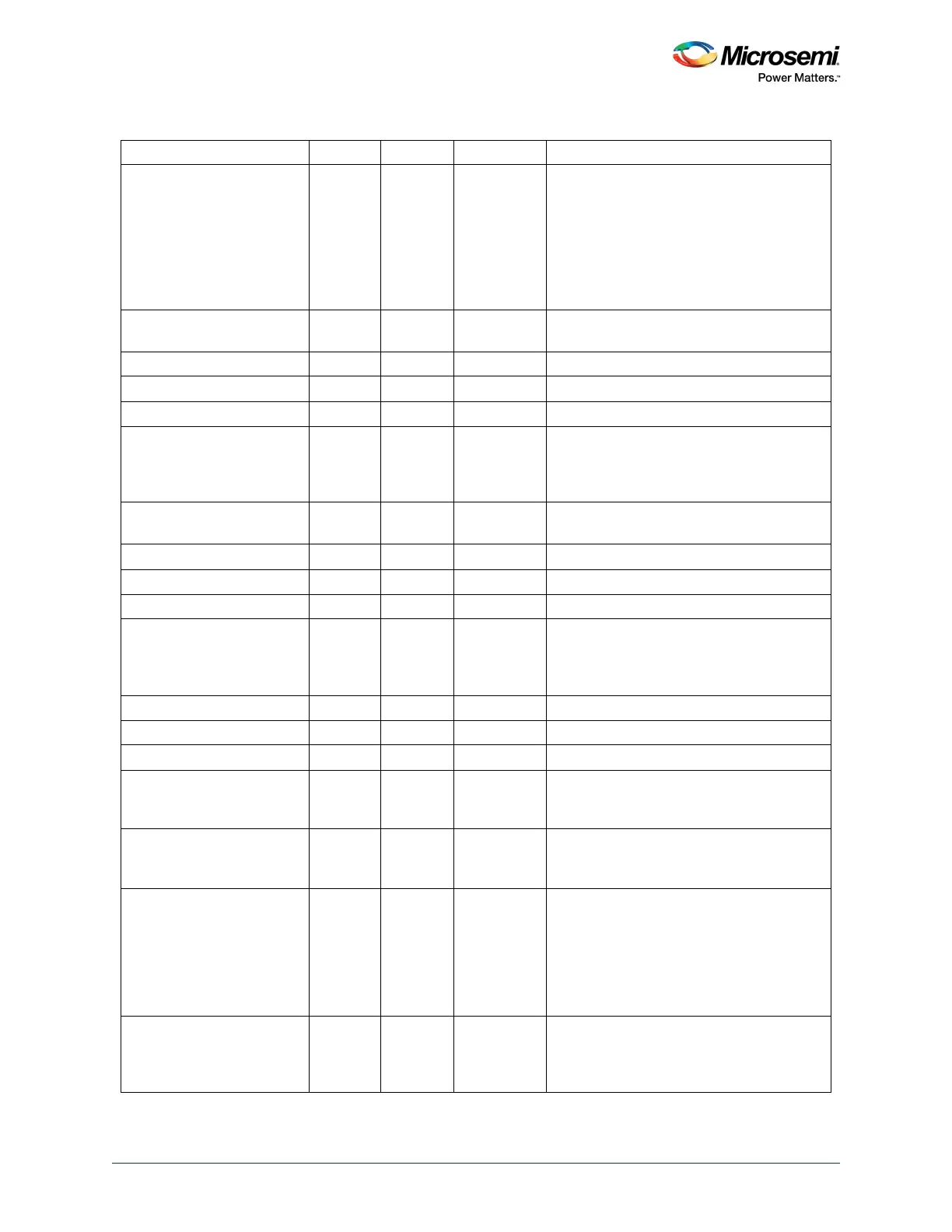

Table 441 • Summary of CAN Controller Registers (continued)

Register Name Address R/W Reset Value Description

Loading...

Loading...