Cortex-M3 Processor (Reference Material)

UG0331 User Guide Revision 15.0 80

3.6.8 Bitfield instructions

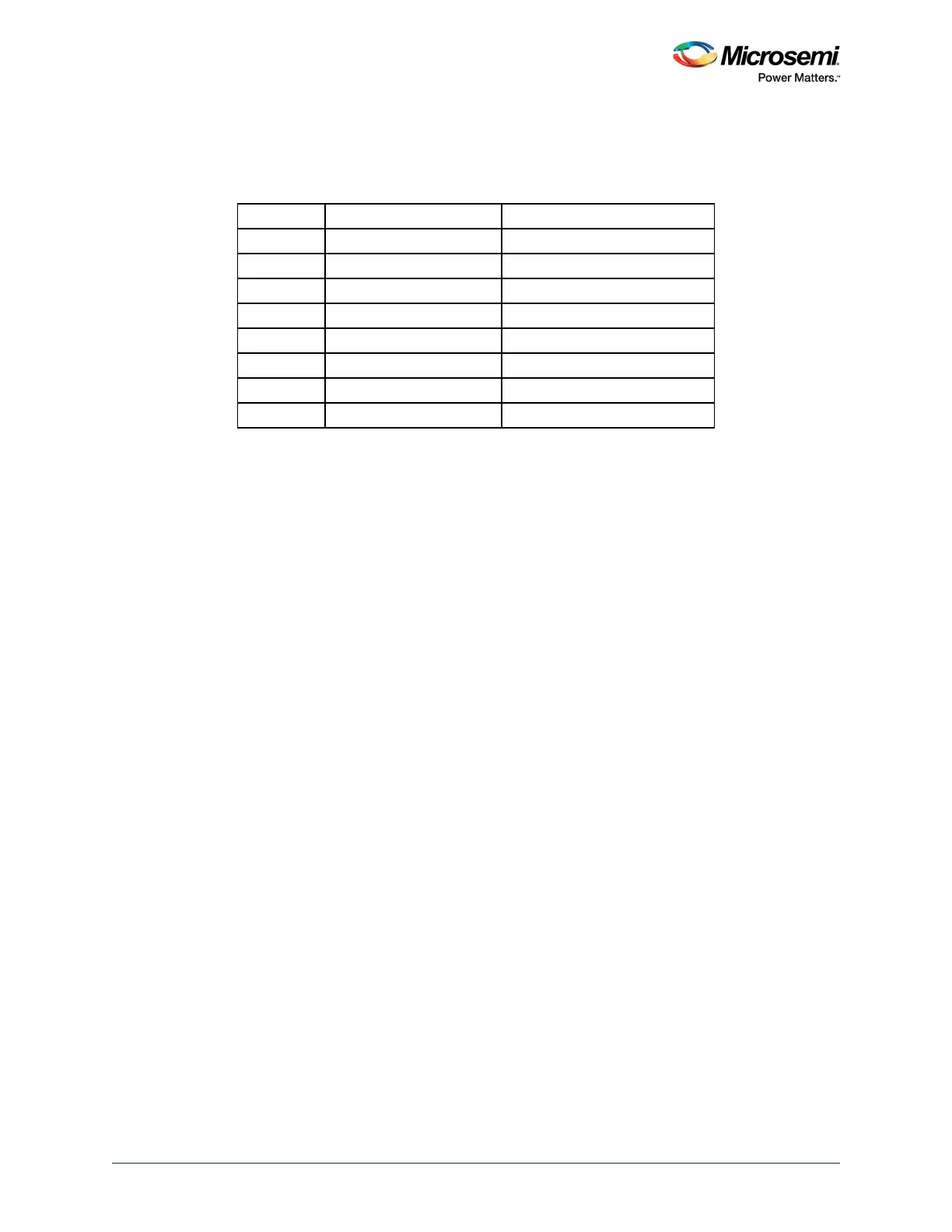

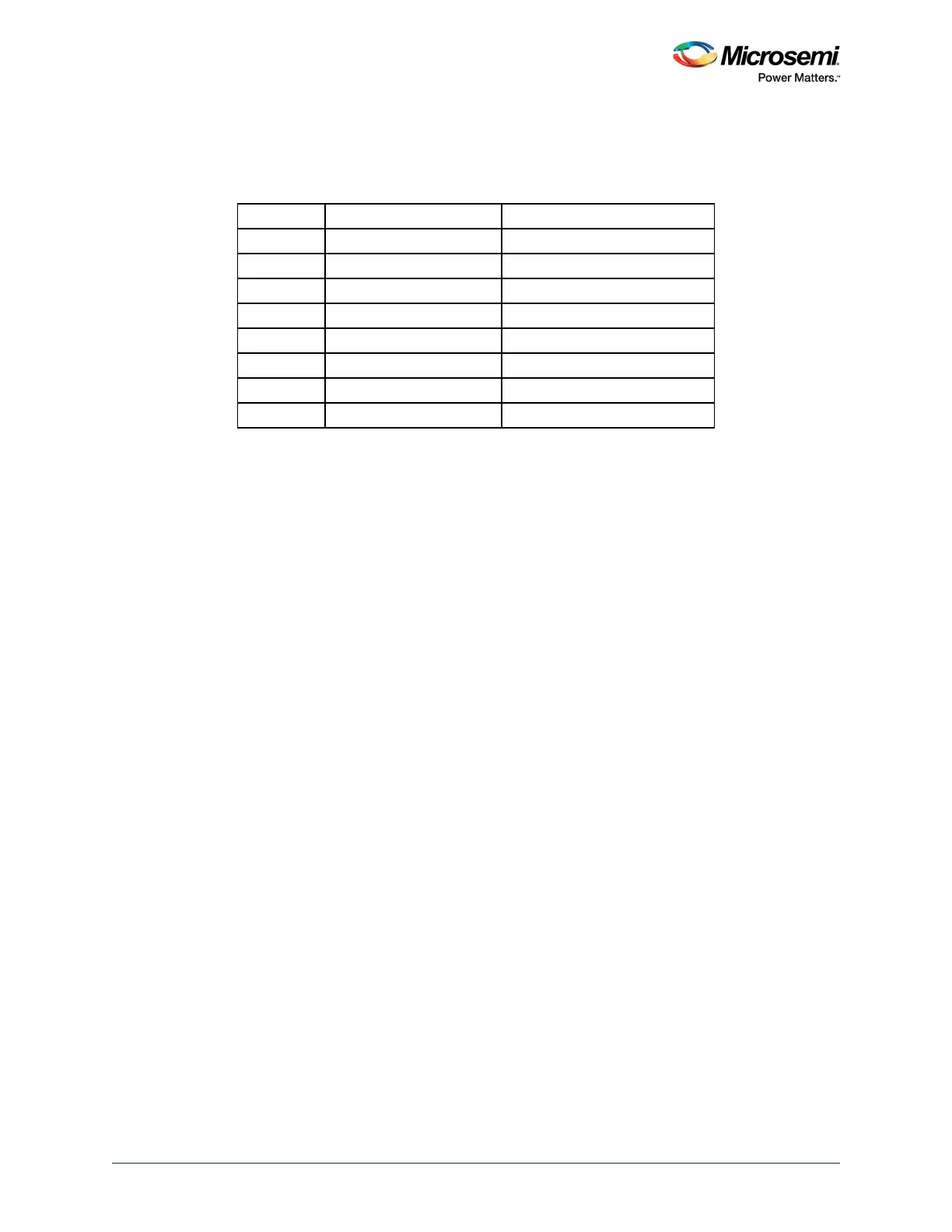

The following table shows the instructions that operate on adjacent sets of bits in registers or bitfields:

3.6.8.1 BFC and BFI

Bit Field Clear and Bit Field Insert.

3.6.8.1.1 Syntax

BFC{cond} Rd, #lsb, #width

BFI{cond} Rd, Rn, #lsb, #width

where:

cond is an optional condition code, see Conditional Execution, page 55.

Rd is the destination register.

Rn is the source register.

lsb is the position of the least significant bit of the bitfield.

lsb

must be in the range 0 to 31.

width is the width of the bitfield and must be in the range 1 to 32-

lsb

.

3.6.8.1.2 Operation

BFC

clears a bitfield in a register. It clears

width

bits in

Rd

, starting at the low bit position

lsb

. Other bits in

Rd

are unchanged.

BFI

copies a bitfield into one register from another register. It replaces

width

bits in

Rd

starting at the low bit

position

lsb

, with

width

bits from

Rn

starting at bit[0]. Other bits in

Rd

are unchanged.

3.6.8.1.3 Restrictions

Do not use SP and do not use PC.

3.6.8.1.4 Condition Flags

These instructions do not affect the flags.

Examples

BFC R4, #8, #12 ; Clear bit 8 to bit 19 (12 bits) of R4 to 0

BFI R9, R2, #8, #12 ; Replace bit 8 to bit 19 (12 bits) of R9 with

; bit 0 to bit 11 from R2.

3.6.8.2 SBFX and UBFX

Signed Bit Field Extract and Unsigned Bit Field Extract.

Table 35 • Packing and Unpacking Instructions

Mnemonic Brief description See

BFC Bit Field Clear

BFC and BFI, page 81

BFI Bit Field Insert

BFC and BFI, page 81

SBFX Signed Bit Field Extract

SBFX and UBFX, page 81

SXTB Sign extend a byte

SXT and UXT, page 82

SXTH Sign extend a halfword

SXT and UXT, page 82

UBFX Unsigned Bit Field Extract

SBFX and UBFX, page 81

UXTB Zero extend a byte

SXT and UXT, page 82

UXTH Zero extend a halfword

SXT and UXT, page 82

Loading...

Loading...