CAN Controller

UG0331 User Guide Revision 15.0 466

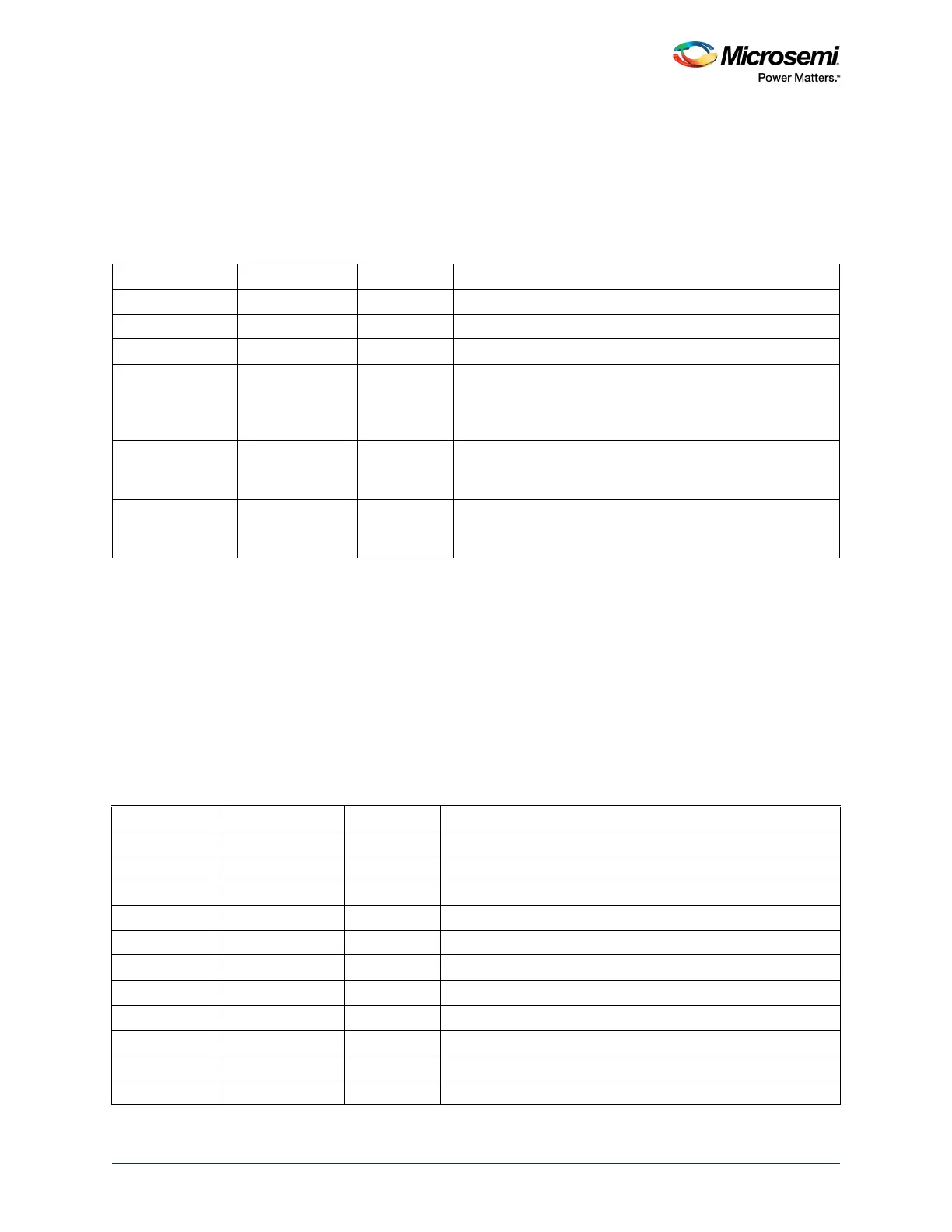

12.6.10 Error Status Register

Status indicators are provided to report the CAN controller error state, receive error count, and transmit

error count. Special flags to report error counter values equal to or in excess of 96 errors are available to

indicate heavily disturbed bus situations.

The following table provides ERROR_STATUS register bit descriptions.

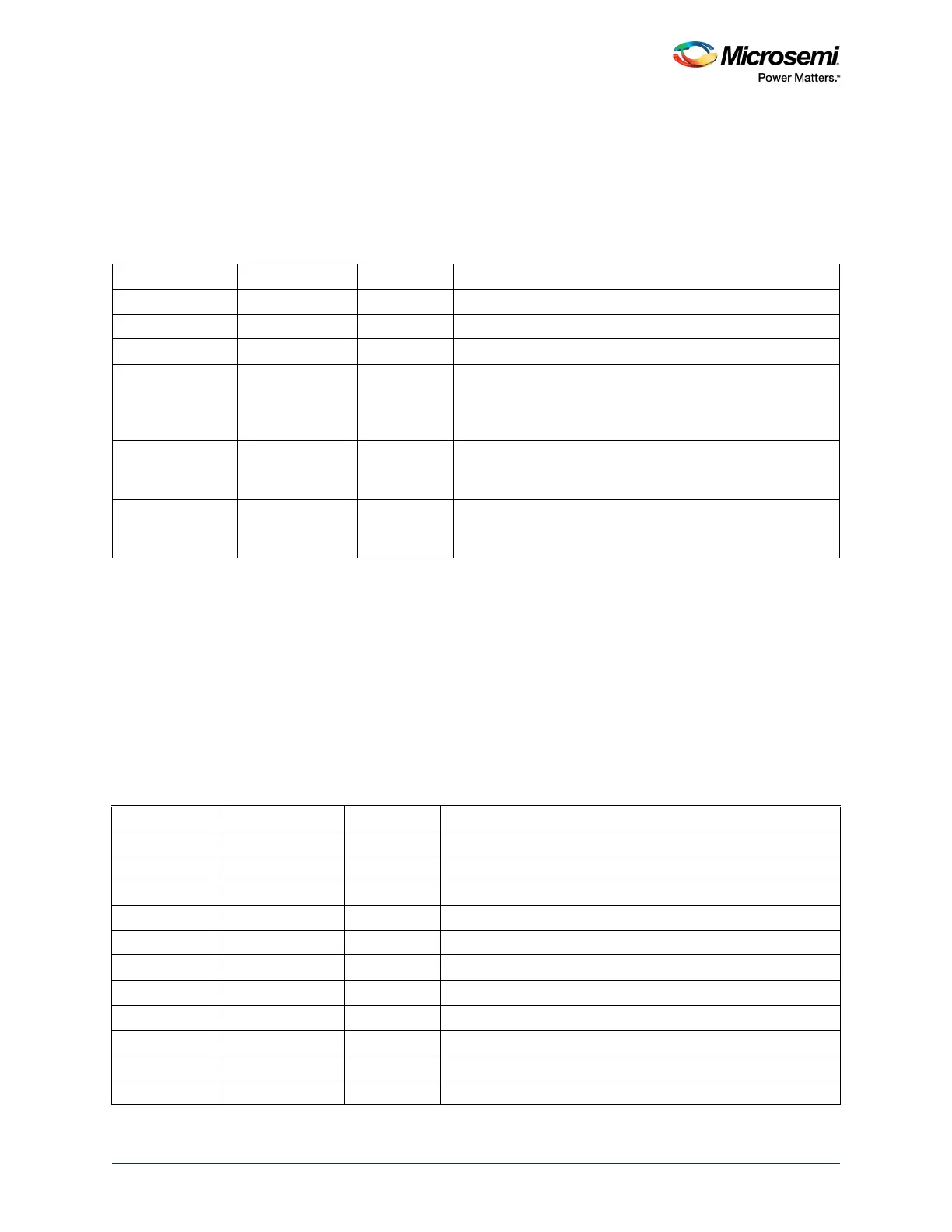

12.6.11 Interrupt Registers

The interrupt controller contains an interrupt enable (INT_ENABLE) and an interrupt status

(INT_STATUS) registers.

12.6.11.1 Interrupt Enable Register

The interrupt enable register controls which particular bits from the interrupt status register are used to

assert the interrupt output int_n. Refer to Interrupt Generation, page 441 for more details. The bits in the

INT_ENABLE register control, which bits in the INT_STATUS register are used to enable the final output,

int_n, interrupt. The Interrupt int_n is asserted if a particular interrupt status bit and the respective enable

bit are set. The following table provides the INT_ENABLE register bit descriptions.

Table 461 • ERROR_STATUS

Bit Number Name Reset Value Description

[31:20] Reserved 0 Reserved

19 rxgte96 0 The receive error counter is greater than or equal to 96 dec.

18 txgte96 0 The transmit error counter is greater than or equal to 96 dec.

[17:16] error_state[1:0] 0 The error state of the CAN mode:

00: error active (normal operation)

01: error passive

1x: bus off

[15:8] rx_err_cnt[7:0] 0 The receive error counter as defined in CAN 2.0 specification.

When in bus-off state, this counter is used to count 128

groups of 11 receive bits.

[7:0] tx_err_cnt[7:0] 0 The transmit error counter as defined in CAN 2.0

specification.

When it is greater than 255 dec, it is fixed at 255 dec.

Table 462 • INT_ENABLE

Bit Number Name Reset Value Description

[31:16] Reserved 0 Reserved

15 sst_failure_enbl 0 Single shot transmission failure interrupt enable.

14 stuck_at_0_enbl 0 Stuck at dominant error interrupt enable.

13 rtr_msg_enbl 0 RTR auto-reply message sent interrupt enable.

12 rx_msg_enbl 0 Receive message available interrupt enable.

11 tx_msg_enbl 0 Message transmitted interrupt enable.

10 rx_msg_loss_enbl 0 Received message lost interrupt enable.

9 bus_off_enbl 0 Bus off interrupt enable.

8 crc_err_enbl 0 CRC error interrupt enable.

7 form_err_enbl 0 Format error interrupt enable.

6 ack_err_enbl 0 Acknowledge error interrupt enable.

Loading...

Loading...