Reset Controller

UG0331 User Guide Revision 15.0 662

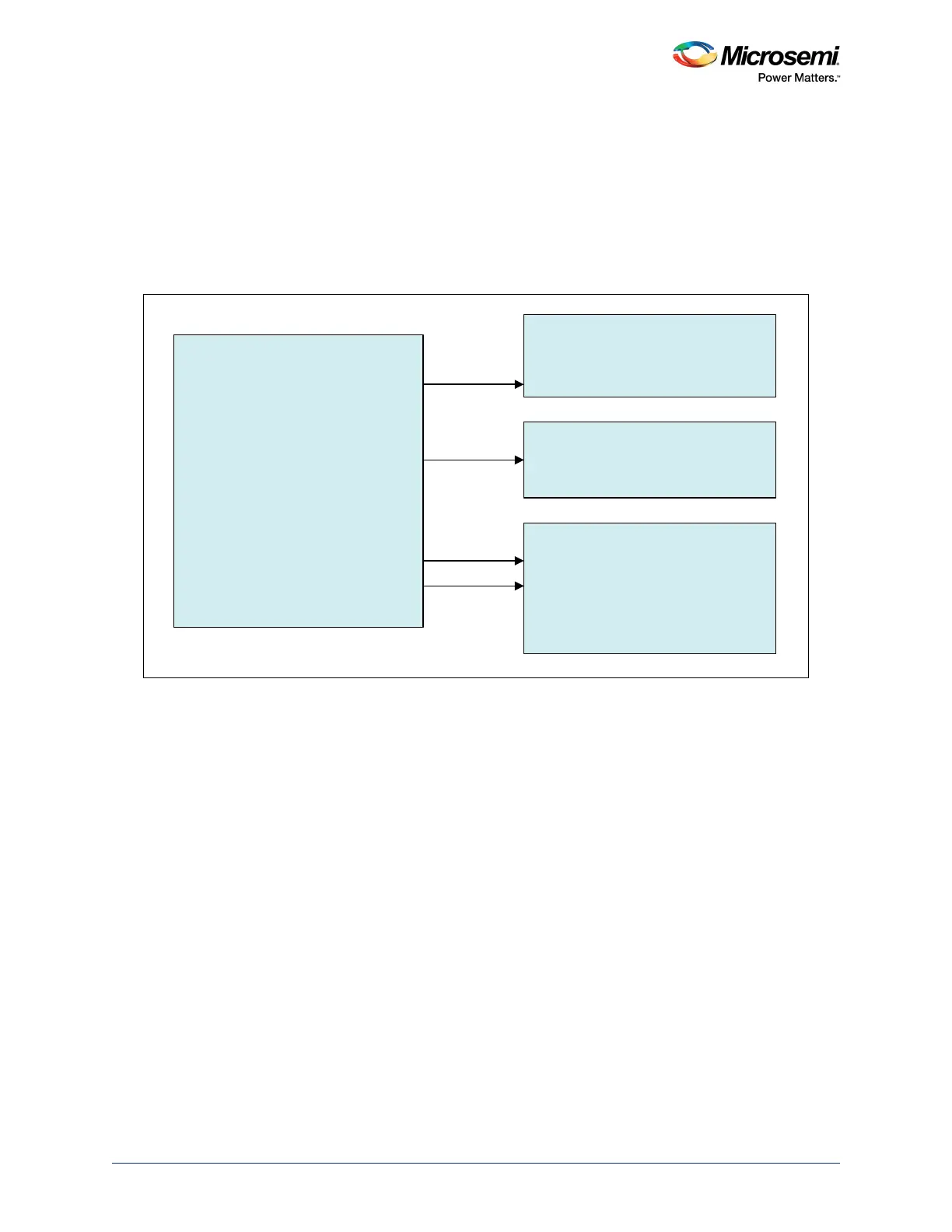

21.3.1.2 Peripheral Initialization

CoreResetP generates reset signals to initialize MDDR, FDDR and SERDES_IF peripheral blocks. The

following figure shows the CoreResetP connectivity with peripheral resets. For each SERDES_IF blocks,

the CoreResetP generates SDIFx_PHY_RESET_N and SDIFx_CORE_RESET_N signals which need to

be connected to SERDES_IF macro on PHY_RESET_N and CORE_RESET_N respectively. For FDDR

and MDDR, the CoreResetP generates CORE reset signals (FDDR_CORE_RESET_N and

MDDR_DDR_AXI_S_CORE_RESET_N).

Figure 297 • CoreResetP Connectivity with Peripheral Resets

0''5B''5B$;,B6B&25(B5(6(7B1

&RUH5HVHW3

6',)[B&25(B5(6(7B1

6',)[B3+<B5(6(7B1

)''5B&25(B5(6(7B1

066

0''5B''5B&25(B5(6(7B1

&25(B5(6(7B1

)''5

6(5'(6B,)B[

&25(B5(6(7B1

3+<B5(6(7B1

Loading...

Loading...