Ethernet MAC

UG0331 User Guide Revision 15.0 413

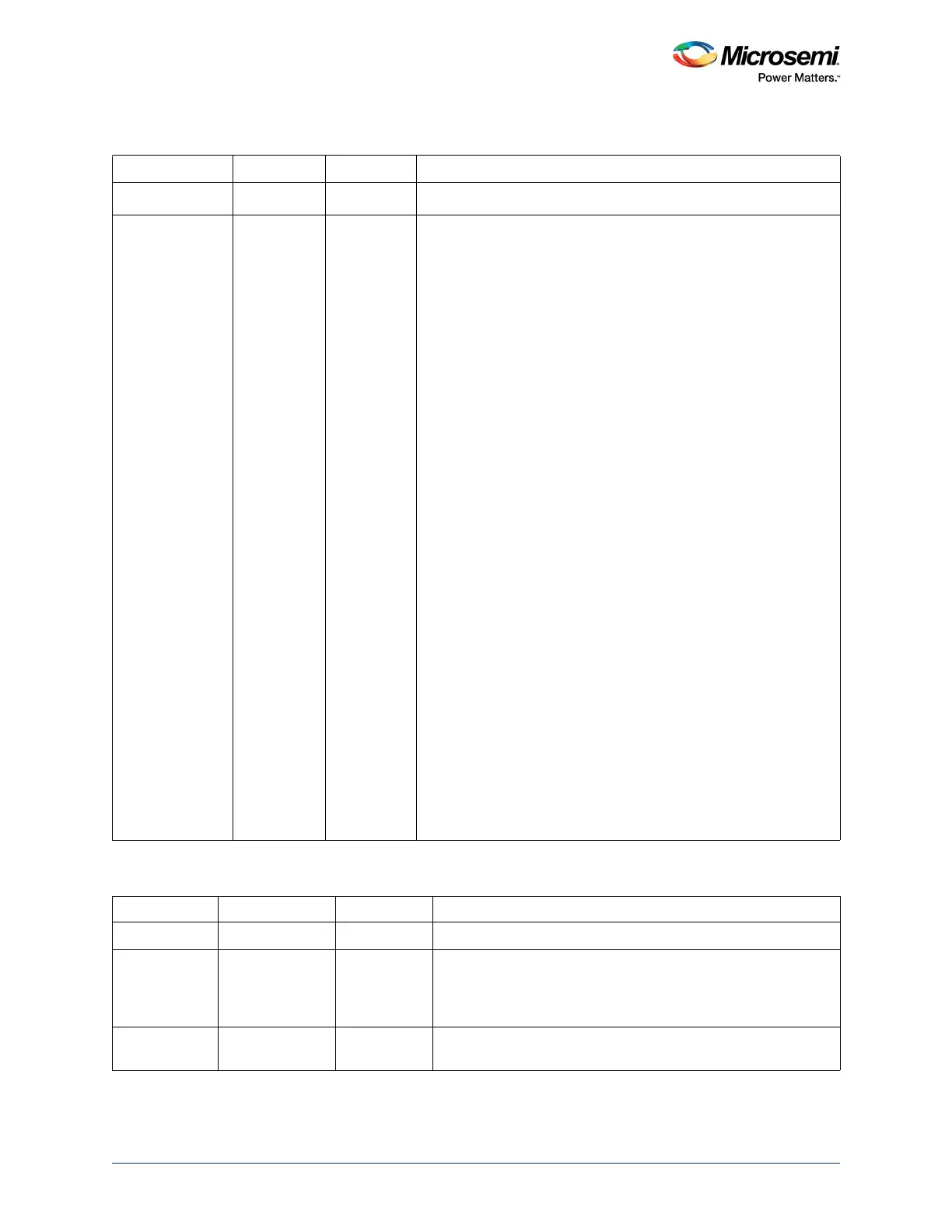

Table 367 • FIFO_CFG4

Bit Number Name Reset Value Description

[31:18] Reserved 0x0 Reserved

[17:0] hstfltrfrm 0x0 These configuration bits are used to signal the drop frame

conditions internal to the A-MCXFIFO.

The bits correspond to the receive statistics vector input to A-

MCXFIFO on a one per one basis. Receive statistics vector

indicates the characteristics of the current receive frame and is

input to A-MCXFIFO.

The setting of this bits along with their don’t care values in the

hstfltrfrmdc not asserted, create the filter that drops the receive

frame if the receive frame does not pass through the acceptable

conditions.

For example, if it is needed to drop a frame that contains a receive

error, least significant fourth bit is set, and all receive frames that

have frame receive error in receive statistics vector asserted are

dropped.

The hstfltrfrm bit and their corresponding receive statistics vector is

as follows:

Bit Description

17:System Receive unicast Address.

16:Truncated Frame.

15:Receive long event.

14:VLAN Tagged frame: frame’s length/type field contained 0x8100

which is the VLAN protocol identifier.

13:Frame was Unsupported Op-code.

12: Frame was a PAUSE control frame

11:Long event detected.

10: Frame contained a dribble nibble.

9: Broadcast address detected

8:Multicast address detected

7: Reception OK

6: Length/Type field was neither a length nor type.

5:Frame’s length field out of range.

4:Frame contained a CRC Error.

3: Frame contained a code error.

2:False carrier previously seen.

1:RX_DV event previously seen.

0:Whether or not a prior packet was dropped.

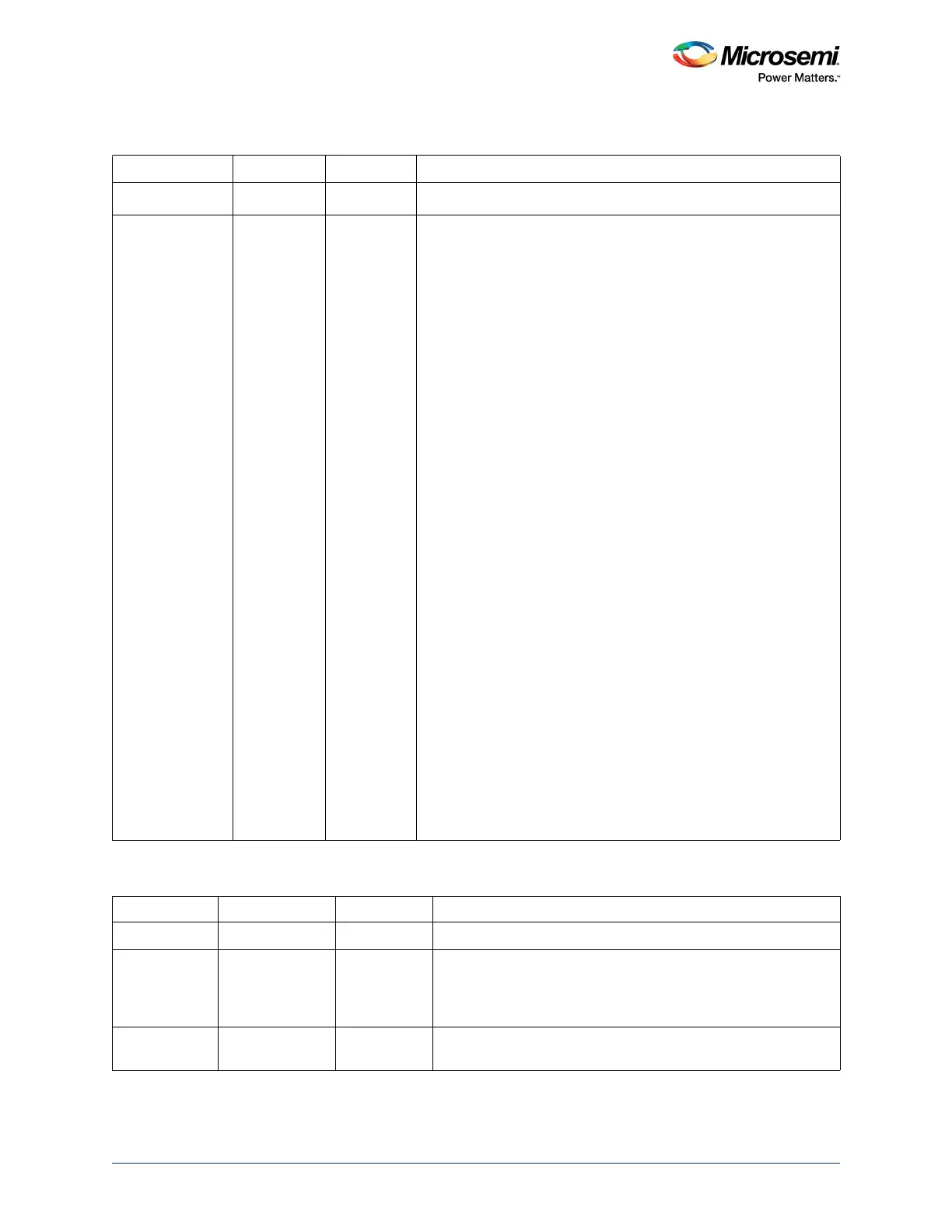

Table 368 • FIFO_CFG5

Bit Number Name Reset Value Description

[31:23] Reserved 0x0 Reserved

22 cfghdplx 0x0 Assertion of this bit configures the A-MCXFIFO to enable the

half duplex as a flow control mechanism. De-assertion of this bit

configures the A-MCXFIFO to enable pause frames as a flow

control mechanism.

21 srfull 0x0 Assertion of this read-only bit indicates that the maximum

capacity of the receive FIFO storage is met or exceeded.

Loading...

Loading...