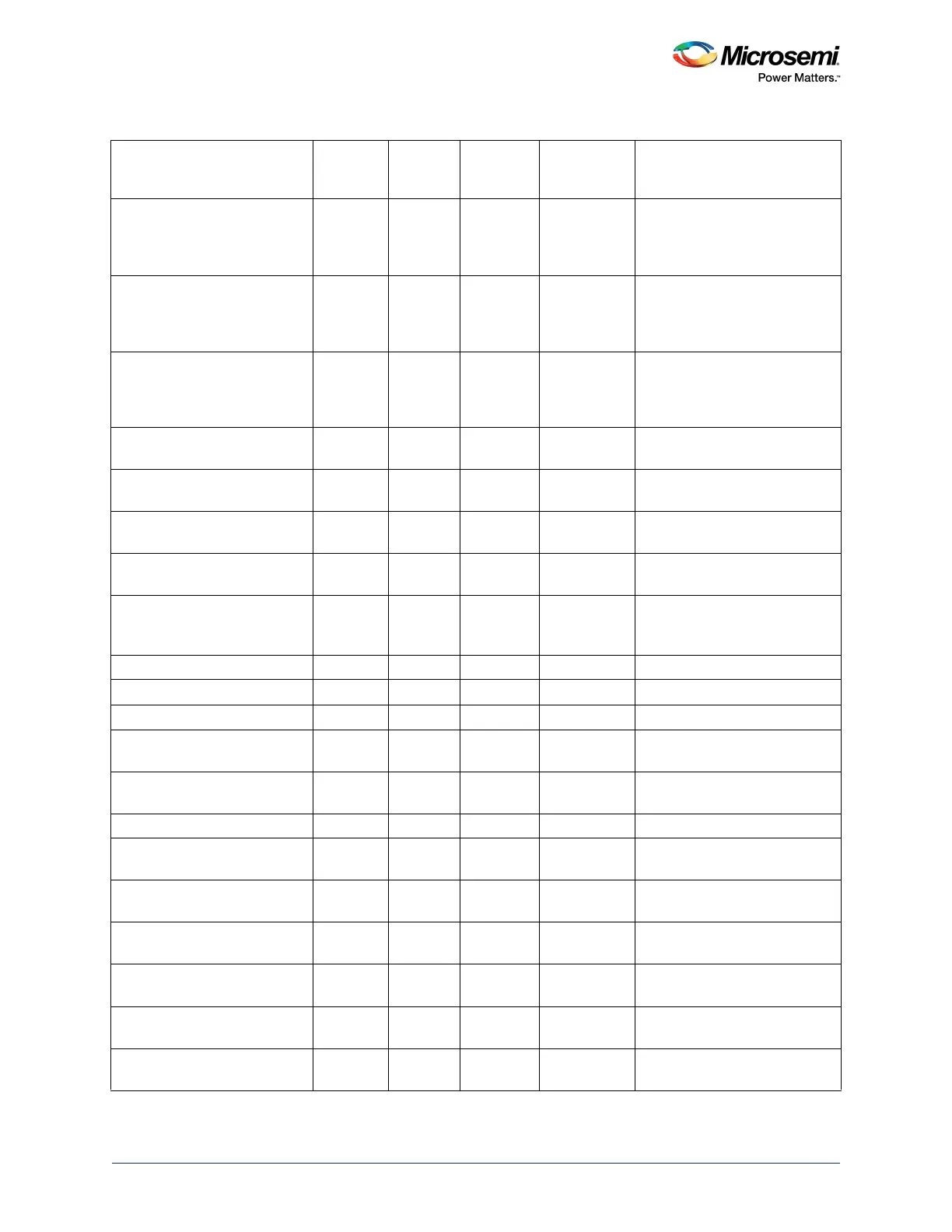

System Register Block

UG0331 User Guide Revision 15.0 680

MM4_5_DDR_FIC_SECURITY

/MM4_5_FIC64_SECURITY

0x128 RO-U SYSRESET_

N

Read and write security for

masters 4, 5, and DDR_FIC to

eSRAM0, eSRAM1, eNVM1,

eNVM0, and MSS DDR bridge

MM3_6_7_8_SECURITY 0x12C RO-U SYSRESET_

N

Read and write security for

masters 3, 6, 7, and 8 to

eSRAM0, eSRAM1, eNVM1,

eNVM0, and MSS DDR bridge

MM9_SECURITY 0x130 RO-U SYSRESET_

N

Read and write security for

master 9 to eSRAM0, eSRAM1,

eNVM1, eNVM0, and MSS DDR

bridge

M3_SR 0x134 RO SYSRESET_

N

Cortex-M3 processor Status

Register

ETM_COUNT_LOW 0x138 RO SYSRESET_

N

ETM count for lower bits [31:0]

ETM_COUNT_HIGH 0x13C RO SYSRESET_

N

ETM count for higher bits

[47:32]

DEVICE_SR 0x140 RO SYSRESET_

N

Device Status Register

ENVM_PROTECT_USER 0x144 RO-U SYSRESET_

N

Configuration for accessibility of

protect regions of eNVM0 and

eNVM1

ENVM_STATUS 0x148 RO-U PORESET_N Code shadow Status Register

DEVICE_VERSION 0x14C RO Configures device version

MSSDDR_PLL_STATUS 0x150 RO MSS DDR PLL Status Register

USB_SR 0x154 RO SYSRESET_

N

USB Status Register

ENVM_SR 0x158 RO SYSRESET_

N

Busy status eNVM0 and eNVM1

Reserved 0x15C

DDRB_STATUS 0x160 RO SYSRESET_

N

MSS DDR bridges status

MDDR_IO_CALIB_STATUS 0x164 RO PORESET_N DDR I/O Calibration Status

Register

MSSDDR_CLK_CALIB_STATU

S

0x168 RO SYSRESET_

N

MSS DDR Clock Calibration

Status Register

WDOGLOAD 0x16C RO-P PORESET_N Configures Watchdog load

value

WDOGMVRP 0x170 RO-P PORESET_N Configures Watchdog MVRP

value

USERCONFIG0 0x174 RO-P SYSRESET_

N

User Configuration Register 0

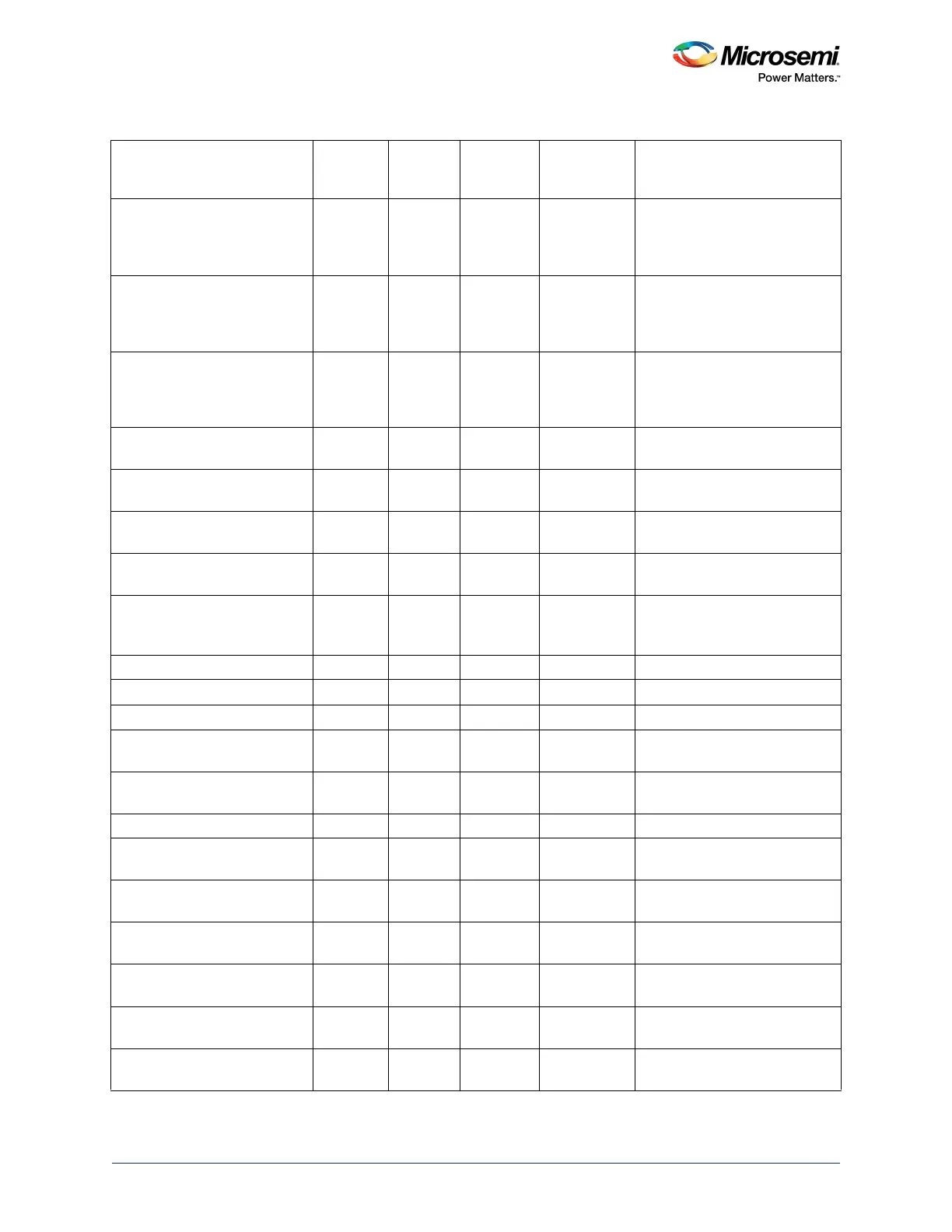

Table 650 • SYSREG (continued)

Register Name

Addr.

Offset

Register

Type

Flash

Write

Protect Reset Source Description

Loading...

Loading...