System Register Block

UG0331 User Guide Revision 15.0 730

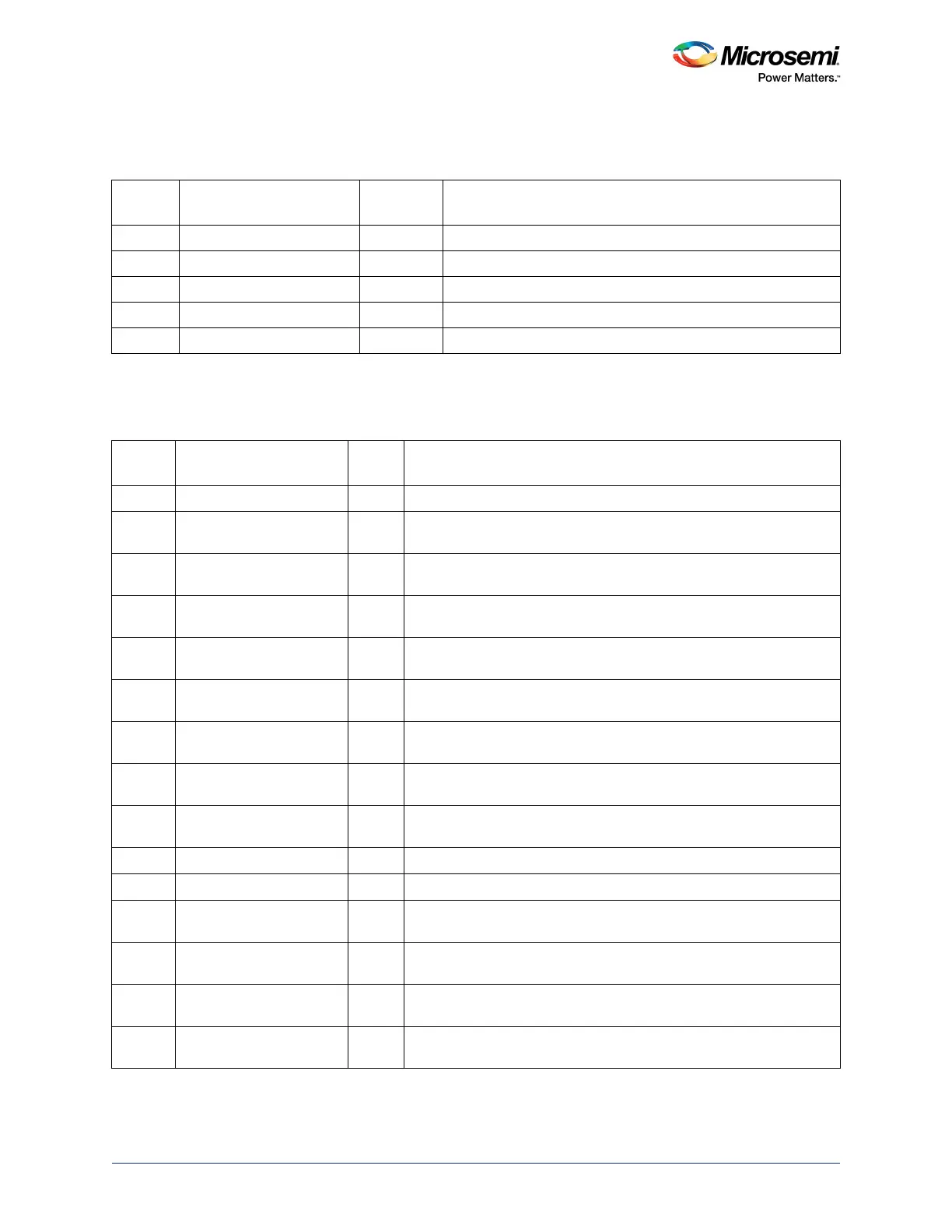

22.3.96 MSS GPIO Definitions

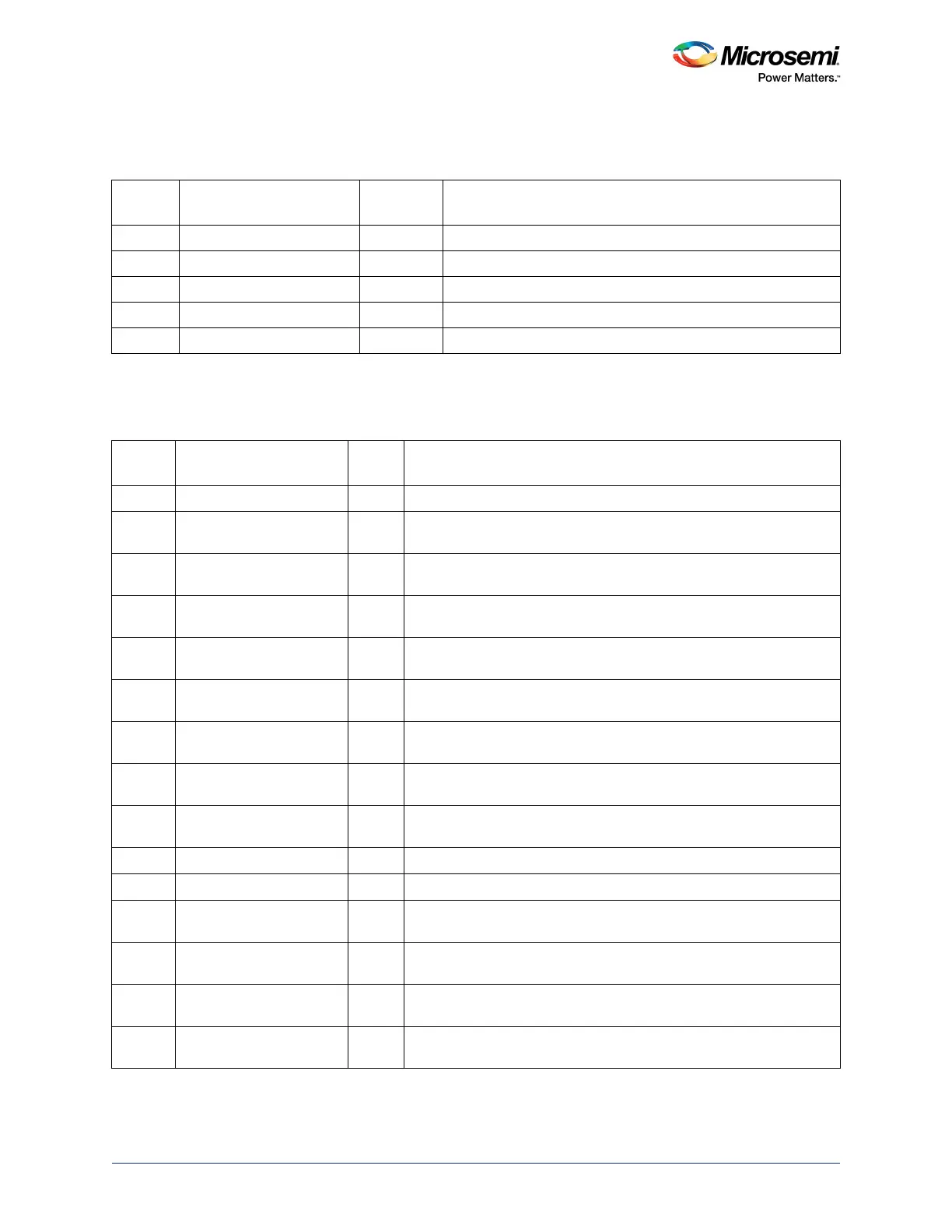

22.3.97 EDAC Status Register

Table 754 • MSS_GPIO_DEF

Bit

Number Name

Reset

Value Description

[31:4] Reserved 0

3 MSS_GPIO_31_24_DEF 0x1 Used to initialize GPIO Bank [31:24] to 0 or 1 after reset.

2 MSS_GPIO_23_16_DEF 0x1 Used to initialize GPIO Bank [23:16] to 0 or 1 after reset.

1 MSS_GPIO_15_8_DEF 0x1 Used to initialize GPIO Bank [15:8] to 0 or 1 after reset.

0 MSS_GPIO_7_0_DEF 0x1 Used to initialize GPIO Bank [7:0] to 0 or 1 after reset.

Table 755 • EDAC_SR

Bit

Number Name

Reset

Value Description

[31:14] Reserved 0

13 CAN_EDAC_2E 0 Updated by CAN when a 2-bit SECDED error has been detected for

RAM memory.

12 CAN_EDAC_1E 0 Updated by CAN when a 1-bit SECDED error has been detected and

is corrected for RAM memory.

11 USB_EDAC_2E 0 Updated by USB when a 2-bit SECDED error has been detected for

RAM memory.

10 USB_EDAC_1E 0 Updated by USB when a 1-bit SECDED error has been detected and

is corrected for RAM memory.

9 MAC_EDAC_RX_2E 0 Updated by Ethernet when a 2-bit SECDED error has been detected

for Rx RAM memory.

8 MAC_EDAC_RX_1E 0 Updated by Ethernet when a 1-bit SECDED error has been detected

and is corrected for Rx RAM memory.

7 MAC_EDAC_TX_2E 0 Updated by Ethernet when a 2-bit SECDED error has been detected

for Tx RAM memory.

6 MAC_EDAC_TX_E 0 Updated by Ethernet when a 1-bit SECDED error has been detected

and is corrected for Tx RAM memory.

5Reserved 0

4Reserved 0

3 ESRAM1_EDAC_2E 0 Updated by the eSRAM_1 controller when a 2-bit SECDED error has

been detected for eSRAM1 memory.

2 ESRAM1_EDAC_1E 0 Updated by the eSRAM_1 Controller when a 1-bit SECDED error has

been detected and is corrected for eSRAM1 memory.

1 ESRAM0_EDAC_2E 0 Updated by the eSRAM_0 controller when a 2-bit SECDED error has

been detected for eSRAM0 memory.

0 ESRAM0_EDAC_1E 0 Updated by the eSRAM_0 controller when a 1-bit SECDED error has

been detected and is corrected for eSRAM0 memory.

Loading...

Loading...