Fabric Interface Interrupt Controller

UG0331 User Guide Revision 15.0 738

23 Fabric Interface Interrupt Controller

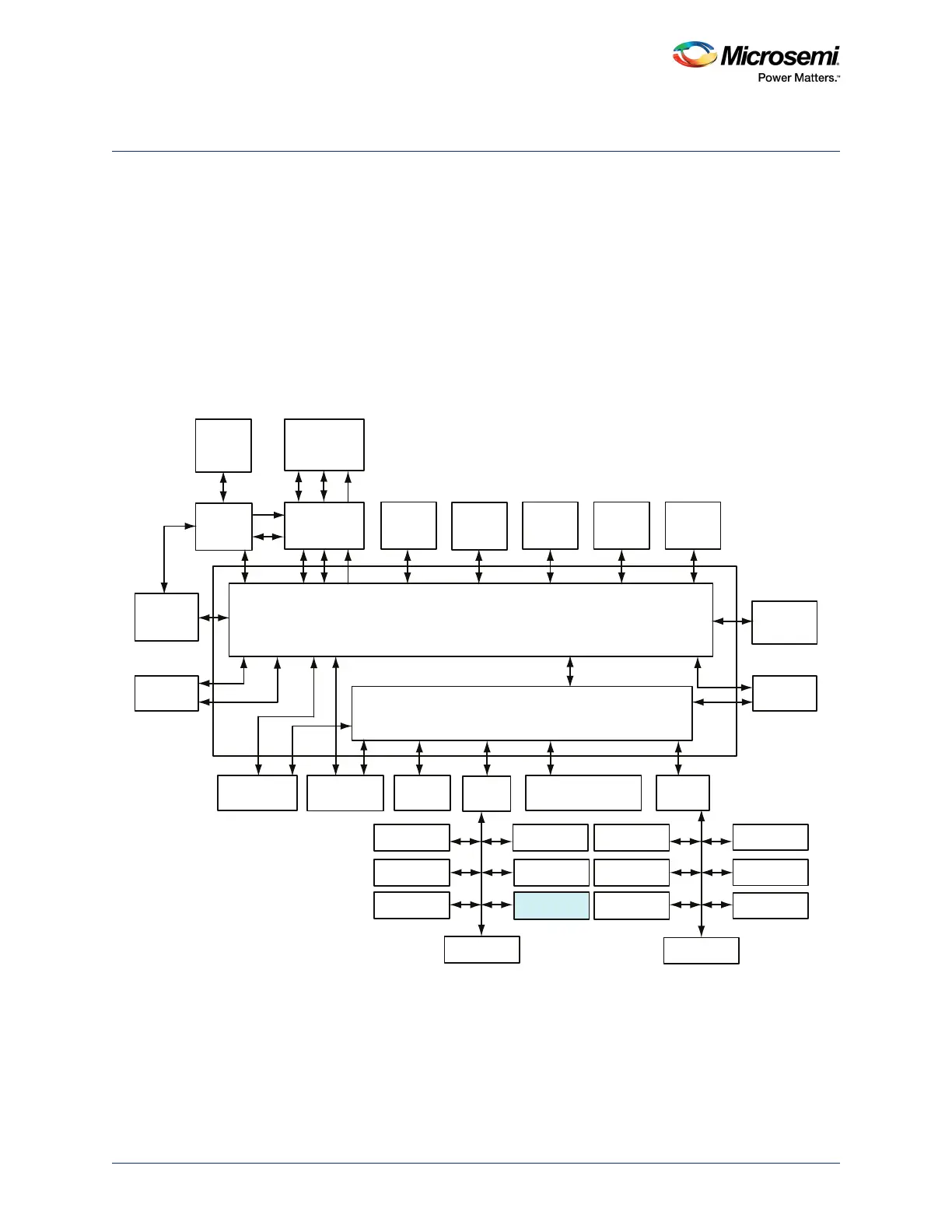

The fabric interface interrupt controller (FIIC) gathers interrupt signals from within the microcontroller

subsystem (MSS) and makes them available to the FPGA fabric. There are a number of peripherals and

other blocks within the MSS that generate interrupt signals. These interrupt signals are connected to the

nested vectored interrupt controller (NVIC) of the Cortex-M3 processor, and can be used as potential

interrupt sources to a user logic within the FPGA fabric.

23.1 Features

• FIIC receives 43 interrupts from the MSS as inputs

• 16 individually configurable MSS to fabric interrupt ports

• 16 individually configurable fabric to MSS interrupt ports

The following figure depicts the connectivity of FIIC to the AHB bus matrix.

Figure 319 • The FIIC Connection to AHB Bus Matrix

AHB Bus Matrix

eSRAM_0

System

Controller

Cache

Controller

SD IC

ARM Cortex-M3

Processor

SDI

MSS DDR

Bridge

PDMA

MS6

MM3

AHB To AHB Bridge with Address Decoder

USB OTG

HPDMA

MDDR

APB_0

SYSREG

Triple Speed

Ethernet MAC

FIC_0

MM4 MS4

MS2 MS3 MS0

MS5

MS1

MM5 MM6

MM7

MM8

MM2 MM1 MM0 MM9

IDC

D/S

eNVM_0 eNVM_1 eSRAM_1

FIC_2 (Peripheral

Initialization)

APB_1

MMUART_0

SPI_0

I2C_0

PDMA

Configuration

WATCHDOG

FIIC

TIMERx2

MMUART_1

SPI_1

I2C_1

GPIO

CAN

RTC

COMM_BLK

FIC_1

MSS_FIC

MS6_USB

MS5_MAC MS5_SR MS5_APB0 MS5_FIC2 MS5_APB1

Loading...

Loading...