Cortex-M3 Processor (Reference Material)

UG0331 User Guide Revision 15.0 57

3.6.3.8 Instruction Width Selection

There are many instructions that can generate either a 16-bit encoding or a 32-bit encoding depending

on the operands and destination register specified. For some of these instructions, you can force a

specific instruction size by using an instruction width suffix. The

.W

suffix forces a 32-bit instruction

encoding. The

.N

suffix forces a 16-bit instruction encoding.

If you specify an instruction width suffix and the assembler cannot generate an instruction encoding of

the requested width, it generates an error.

Note: In some cases it might be necessary to specify the

.W

suffix, for example if the operand is the label of an

instruction or literal data, as in the case of branch instructions. This is because the assembler might not

automatically generate the right size encoding.

To use an instruction width suffix, place it immediately after the instruction mnemonic and condition code,

if any. The following example shows instructions with the instruction width suffix.

Example 3

Instruction width selection

BCS.W label ; creates a 32-bit instruction even for a short branch

ADDS.W R0, R0, R1 ; creates a 32-bit instruction even though the same

; operation can be done by a 16-bit instruction

3.6.4 Memory Access Instructions

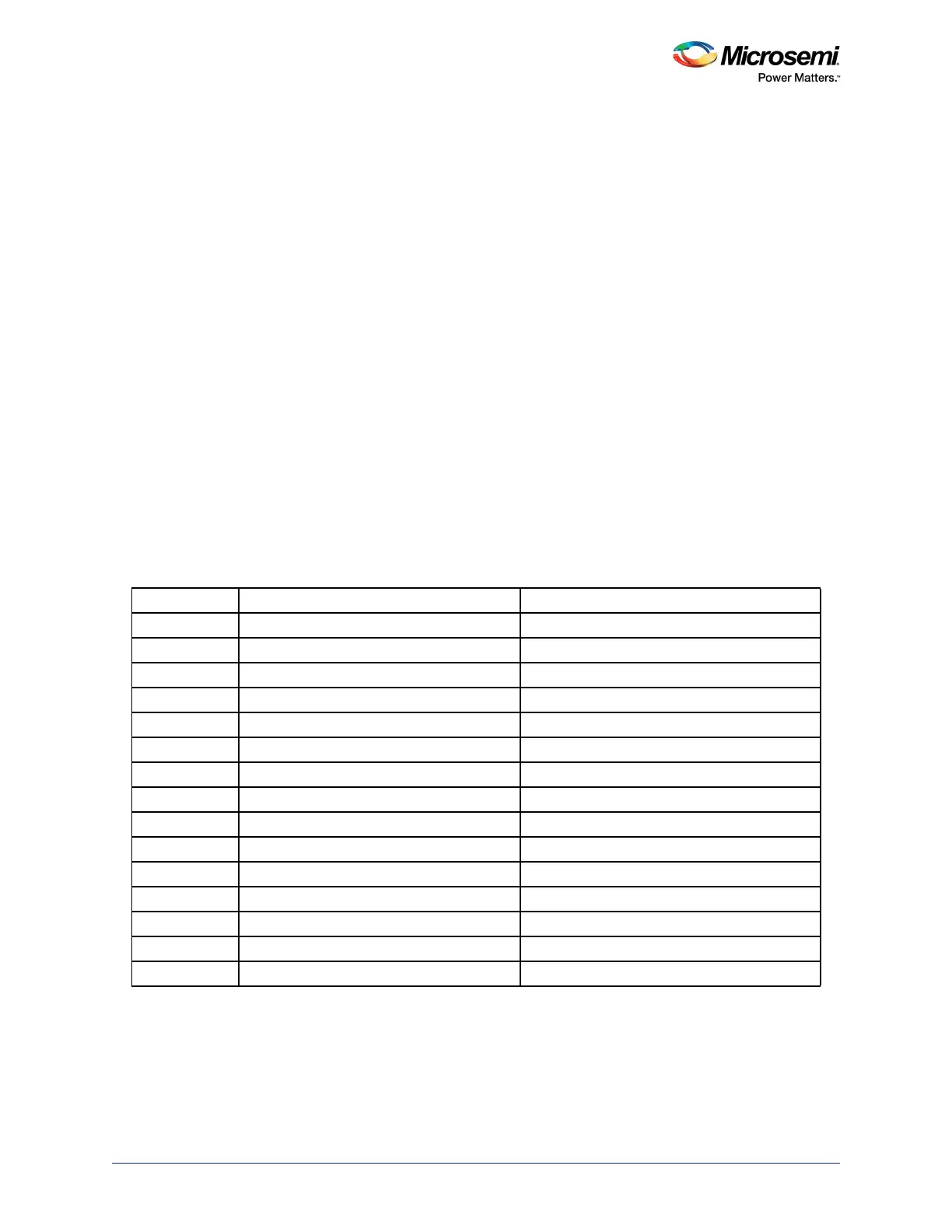

The following table provides memory access instructions:

Table 30 • Memory Access Instructions

Mnemonic Brief Description See

ADR Generate PC-relative address ADR, page 59

CLREX Clear Exclusive CLREX, page 67

LDM{mode} Load Multiple registers LDM and STM, page 64

LDR{type} Load Register using immediate offset LDR and STR, Immediate Offset, page 59

LDR{type} Load Register using register offset LDR and STR, Register Offset, page 61

LDR{type}T Load Register with unprivileged access LDR and STR, Unprivileged, page 62

LDR Load Register using PC-relative address LDR, PC-relative, page 63

LDREX{type} Load Register Exclusive LDREX and STREX, page 66

POP Pop registers from stack PUSH and POP, page 65

PUSH Push registers onto stack PUSH and POP, page 65

STM{mode} Store Multiple registers LDM and STM, page 64

STR{type} Store Register using immediate offset LDR and STR, Immediate Offset, page 59

STR{type} Store Register using register offset LDR and STR, Register Offset, page 61

STR{type}T Store Register with unprivileged access LDR and STR, Unprivileged, page 62

STREX{type} Store Register Exclusive LDREX and STREX, page 66

Loading...

Loading...