Embedded NVM (eNVM) Controllers

UG0331 User Guide Revision 15.0 179

Note: Refer to Table Table 99, page 162 for information on different masters.

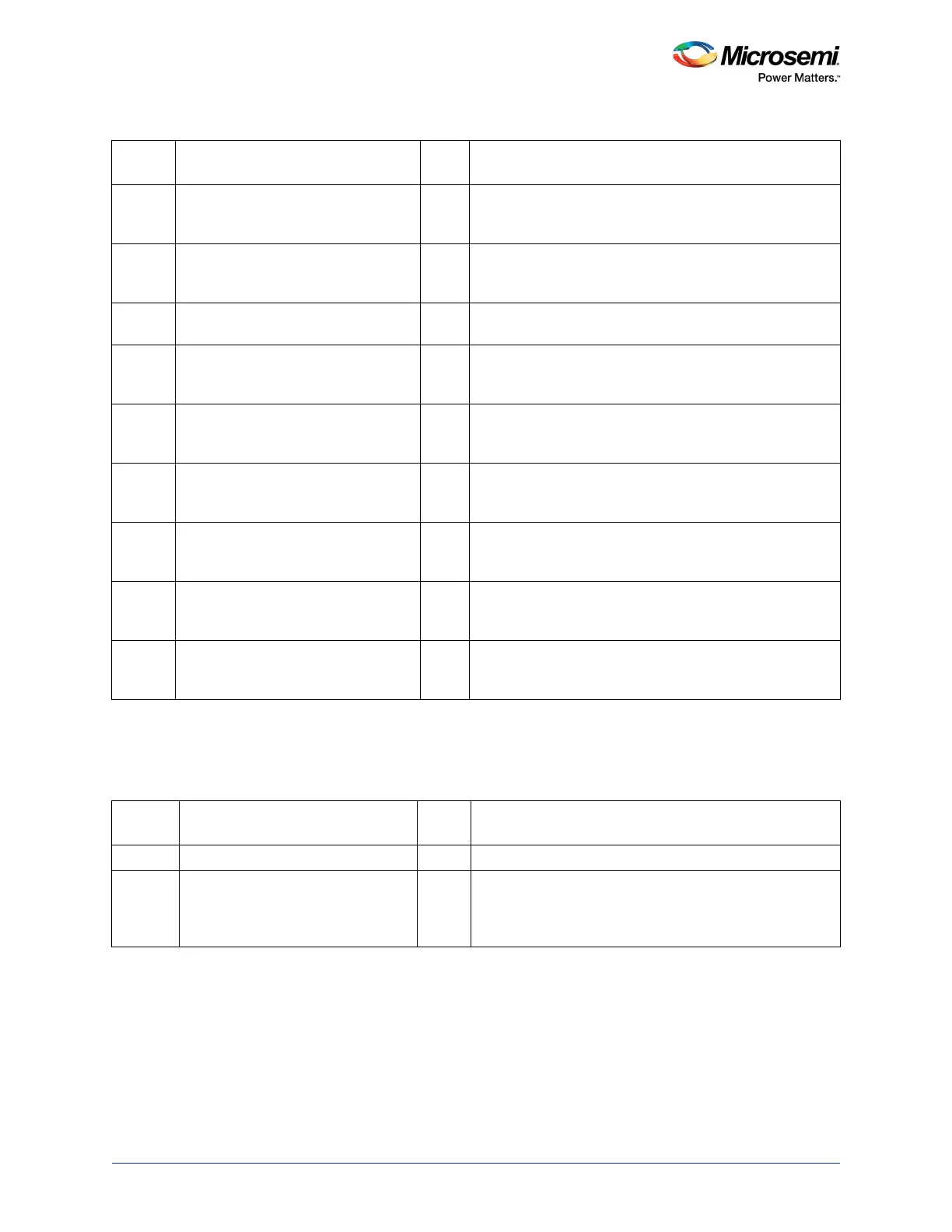

8 NVM1_LOWER_M3ACCESS 0x1 When this bit is set, it indicates that the M3 can access the

lower protection region of eNVM1. This will be set by the

user flash row bit.

7 NVM0_UPPER_WRITE_ALLOWED 0x1 When set indicates that the masters who have read access

can have write access to the upper protection region of

eNVM0. This will be set by the user flash row bit.

6 NVM0_UPPER_OTHERS_ACCESS 0x1 When set indicates that the other masters can access the

upper protection region of eNVM0.

5 NVM0_UPPER_FABRIC_ACCESS 0x1 When set indicates that the fabric can access the upper

protection region of eNVM0. This will be set by the user

flash row bit.

4 NVM0_UPPER_M3ACCESS 0x1 When this bit is set, it indicates that the M3 can access the

upper protection region of eNVM0. This will be set by the

user flash row bit.

3 NVM0_LOWER_WRITE_ALLOWED 0x1 When set indicates that the masters who have read access

can have write access to the lower protection region of

eNVM0. This will be set by the user flash row bit.

2 NVM0_LOWER_OTHERS_ACCESS 0x1 When set indicates that the other masters can access the

lower protection region of eNVM0. This will be set by the

user flash row bit.

1 NVM0_LOWER_FABRIC_ACCESS 0x1 When set indicates that the fabric can access the lower

protection region of eNVM0. This will be set by the user

flash row bit.

0 NVM0_LOWER_M3ACCESS 0x1 When this bit is set, it indicates that the M3 can access the

lower protection region of eNVM0. This will be set by the

user flash row bit.

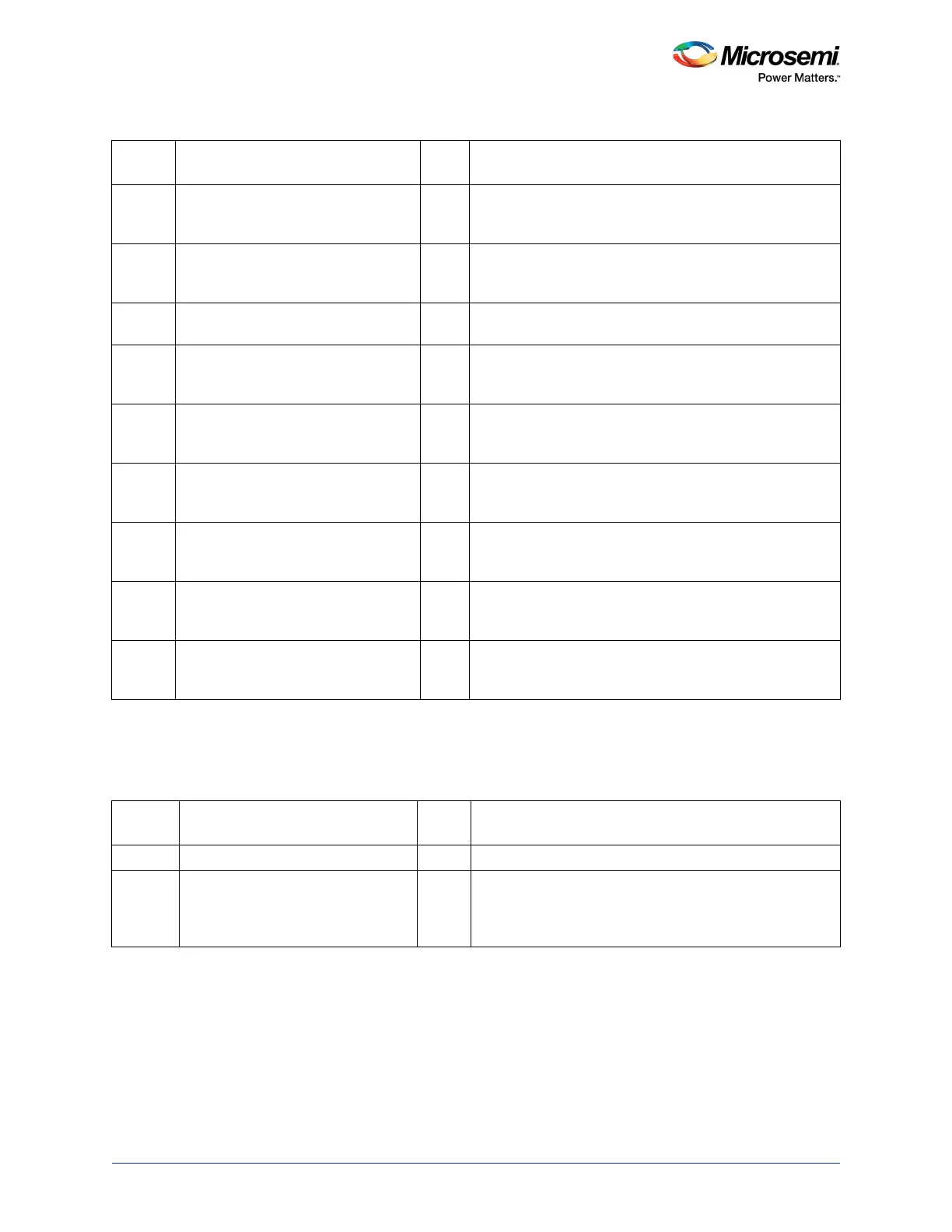

Table 109 • ENVM_STATUS

Bit

Number Name

Reset

Value Description

[31:1] Reserved 0

0 CODE_SHADOW_EN 0 Read by the system controller during device start-up, to

indicate whether the user has configured the device such

that code shadowing is to be performed by system

controller firmware.

Table 108 • ENVM_PROTECT_USER (continued)

Bit

Number Name

Reset

Value Description

Loading...

Loading...