request to the MSS DDR bridge. A soft SDRAM memory controller implemented in the fabric can be

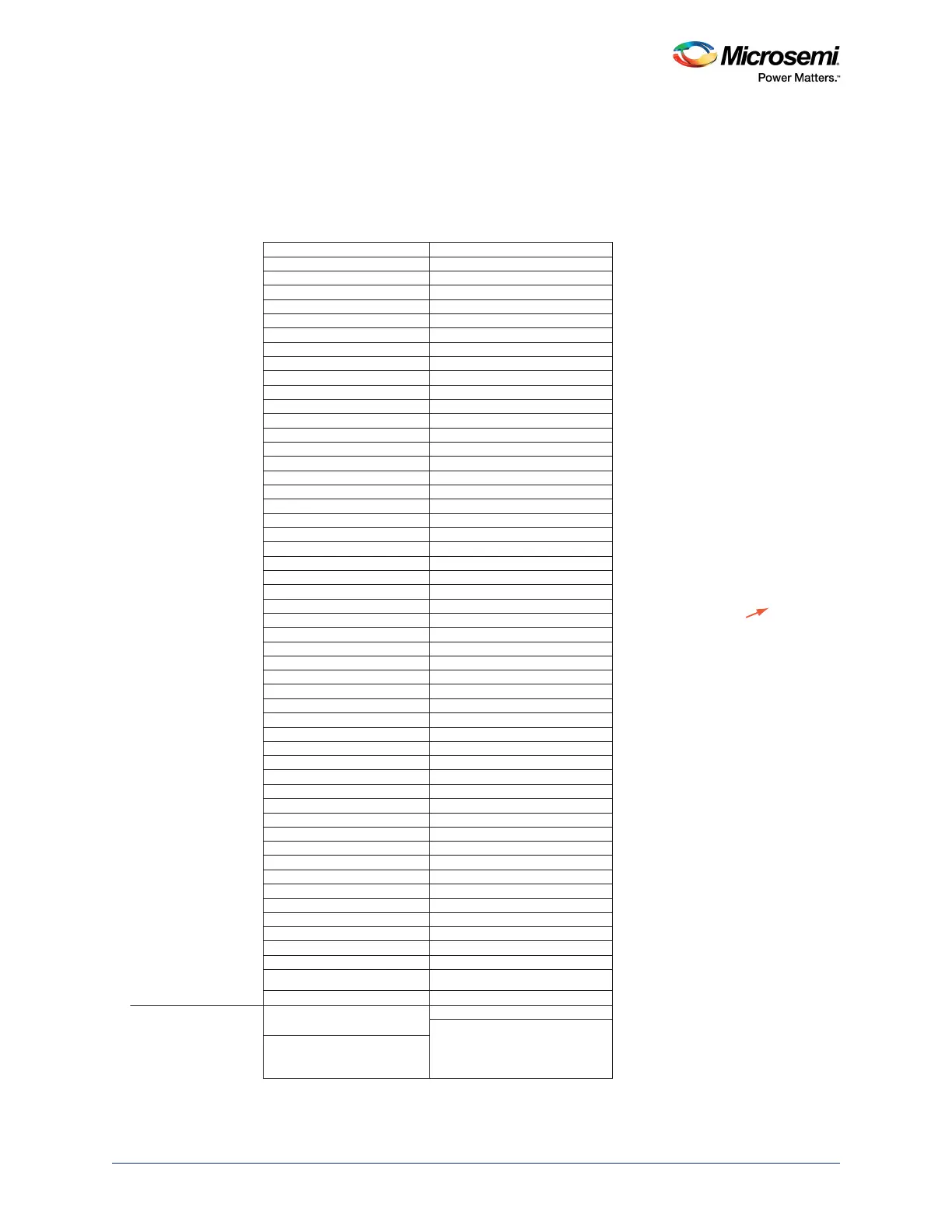

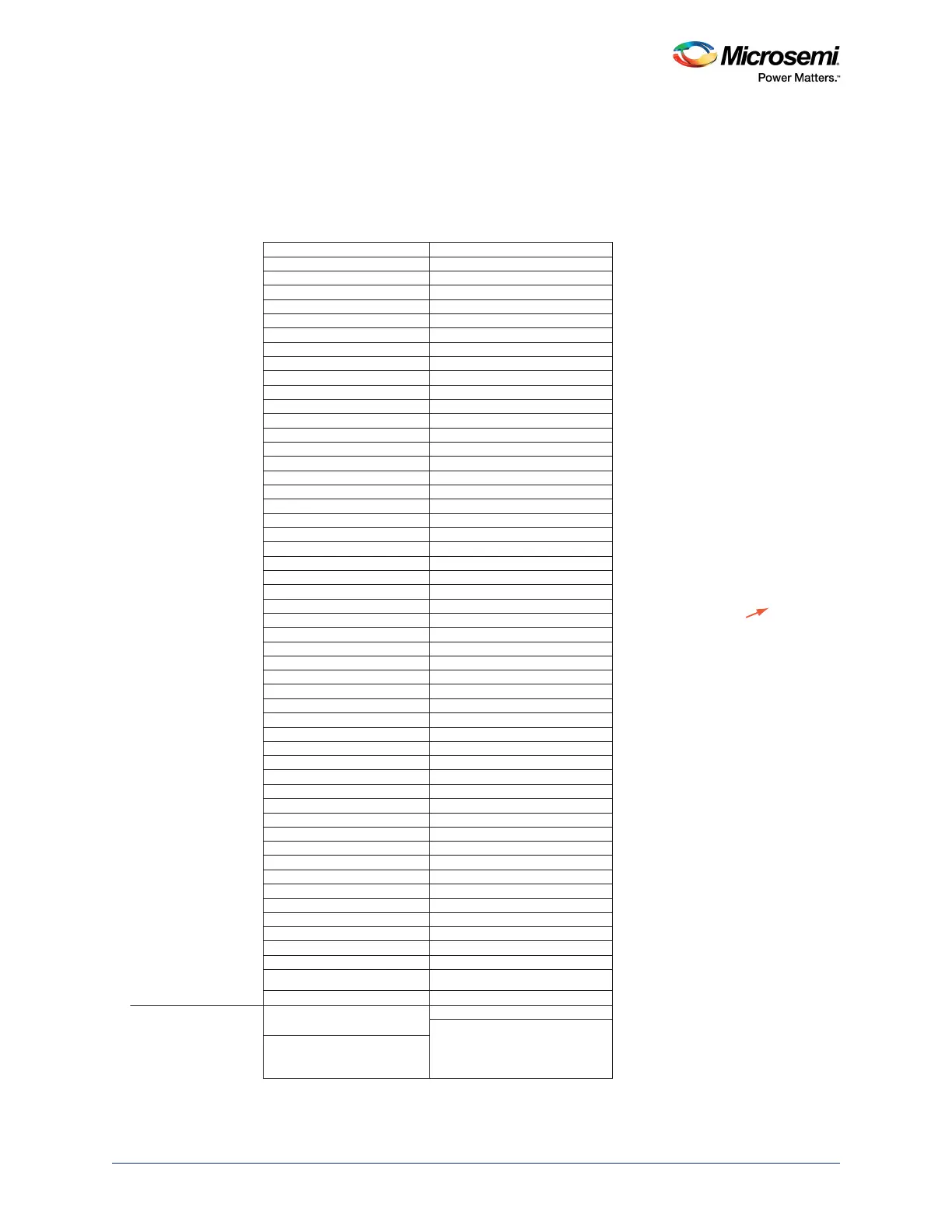

Memory Map of

Cortex-M3 Processor

Memory Map of System

Controller, FPGA Fabric

Master, Ethernet MAC,

Peripheral DMA

FPGA Fabric FIC Region5 FPGA Fabric FIC Region5 0xF0000000 - 0xFFFFFFFF

0xE0000000 - 0xEFFFFFFF

MDDR Space 3 DDR_0 Space 3 0xD0000000 - 0xDFFFFFFF

MDDR Space 2 DDR_0 Space 2 0xC0000000 - 0xCFFFFFFF

MDDR Space 1 DDR_0 Space 1 0xB0000000 - 0xBFFFFFFF

MDDR Space 0 DDR_0 Space 0 0xA0000000 - 0xAFFFFFFF

FPGA Fabric FIC Region4 FPGA Fabric FIC Region4 0x90000000 - 0x9FFFFFFF

FPGA Fabric FIC Region3 FPGA Fabric FIC Region3 0x80000000 - 0x8FFFFFFF

FPGA Fabric FIC Region2 FPGA Fabric FIC Region2 0x70000000 - 0x7FFFFFFF

0x60100000 - 0x6FFFFFFF

AHB-to-eNVM_1 Registers AHB-to-eNVM_1 Registers 0x600C0000 - 0x600FFFFF

AHB-to-eNVM_0 Registers AHB-to-eNVM_0 Registers 0x60080000 - 0x600BFFFF

eNVM_1 eNVM_1 0x60040000 - 0x6007FFFF

eNVM_0 eNVM_0 0x60000000 - 0x6003FFFF

FPGA Fabric FIC Region1 FPGA Fabric FIC Region1 0x50000000 - 0x5FFFFFFF

Peripheral Bit-band

alias region of Cortex-M3

processor

0x44000000 - 0x4FFFFFFF

Peripherals (BB View) 0x42000000 - 0x43FFFFFF

0x40410000 - 0x41FFFFFF

Cache Back door 0x40400000 - 0x4040FFFF

0x40044000 - 0x403FFFFF

USB USB 0x40043000 - 0x40043FFF

0x40042000 - 0x40042FFF

Ethernet MAC Control Ethernet MAC Control 0x40041000 - 0x40041FFF

0x40039000 - 0x40040FFF

SYSREG SYSREG 0x40038000 - 0x40038FFF

(63 K space

allocation

for devices

outside MSS)

0x40030000 - 0x40037FFF

Config DDR_1, PCIe_0, PCIe_1, etc. Config DDR_1, PCIe_0, PCIe_1, etc. 0x40020400 - 0x4002FFFF

Config DDR_0 Config DDR_0 0x40020000 - 0x400203FF

0x40018000 - 0x4001FFFF

RTC RTC 0x40017000 - 0x40017FFF

COMBLK COMBLK 0x40016000 - 0x40016FFF

CAN CAN 0x40015000 - 0x40015FFF

High Performance DMA High Performance DMA 0x40014000 - 0x40014FFF

MSS GPIO MSS GPIO 0x40013000 - 0x40013FFF

I2C_1 I2C_1 0x40012000 - 0x40012FFF

SPI_1 SPI_1 0x40011000 - 0x40011FFF

UART_1 UART_1 0x40010000 - 0x40010FFF

0x40007000 - 0x4000FFFF

Fabric Interface Interrupt Controller Fabric Interface Interrupt Controller

0x40006000 - 0x40006FFF

Watchdog

Watchdog 0x40005000 - 0x40005FFF

Timer Timer 0x40004000 - 0x40004FFF

Peripheral DMA Control Peripheral DMA Control 0x40003000 - 0x40003FFF

I2C_0 I2C_0 0x40002000 - 0x40002FFF

SPI_0 SPI_0 0x40001000 - 0x40001FFF

UART_0 UART_0 0x40000000 - 0x40000FFF

FPGA Fabric FIC Region0 FPGA Fabric FIC Region0 0x30000000 - 0x3FFFFFFF

SRAM bit-band alias

region of Cortex-M3

processor

0x24000000 - 0x2FFFFFFF

eSRAM_0/eSRAM_1(BB View) 0x22000000 - 0x23FFFFFF

0x20014000 - 0x21FFFFFF

ECC eSRAM_1 ECC eSRAM_1 0x20012000 - 0x20013FFF

ECC eSRAM_0 ECC eSRAM_0 0x20010000 - 0x20011FFF

Cortex-M3 processor system

region

eSRAM_1 eSRAM_1 0x20008000 - 0x2000FFFF

eSRAM_0 eSRAM_0 0x20000000 - 0x20007FFF

Cortex-M3 processor code

region

0x10000000 - 0x1FFFFFFF

MDDR Space 1 (mirrored)

0x00080000 - 0x1FFFFFFF

eNVM (Fabric) virtual view

0x0007FFFF

Visible only

to FPGA

fabric master

MDDR Space 0 (mirrored)

0x00000000 - 0x0000FFFF

0x00000000

{

{

}

Loading...

Loading...