AHB Bus Matrix

UG0331 User Guide Revision 15.0 212

• Read by an enabled master to any slave that is not R or RW

• Read by an enabled master to addresses not corresponding to a slave

• Read by the fabric master to the protected region

• Read by a disabled master to any location

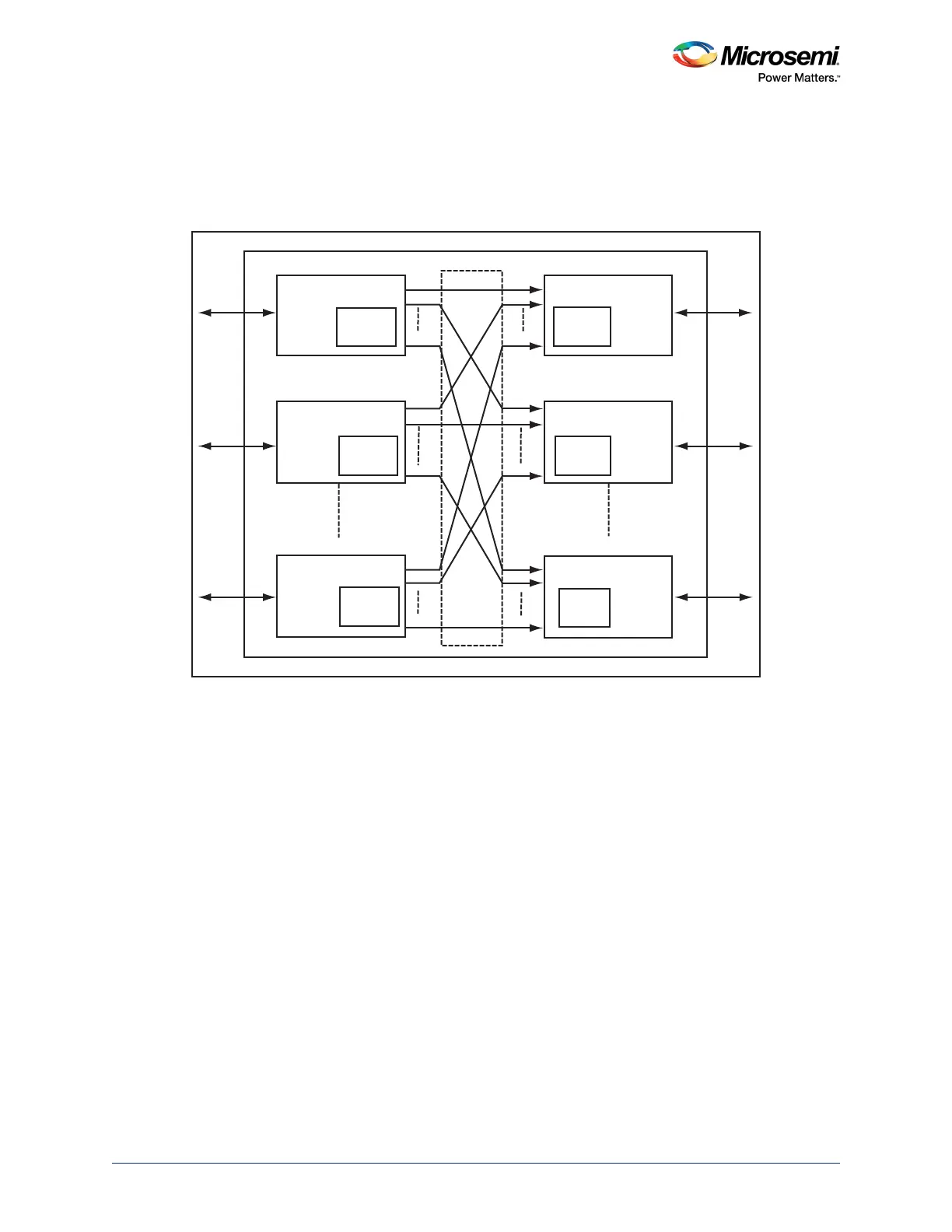

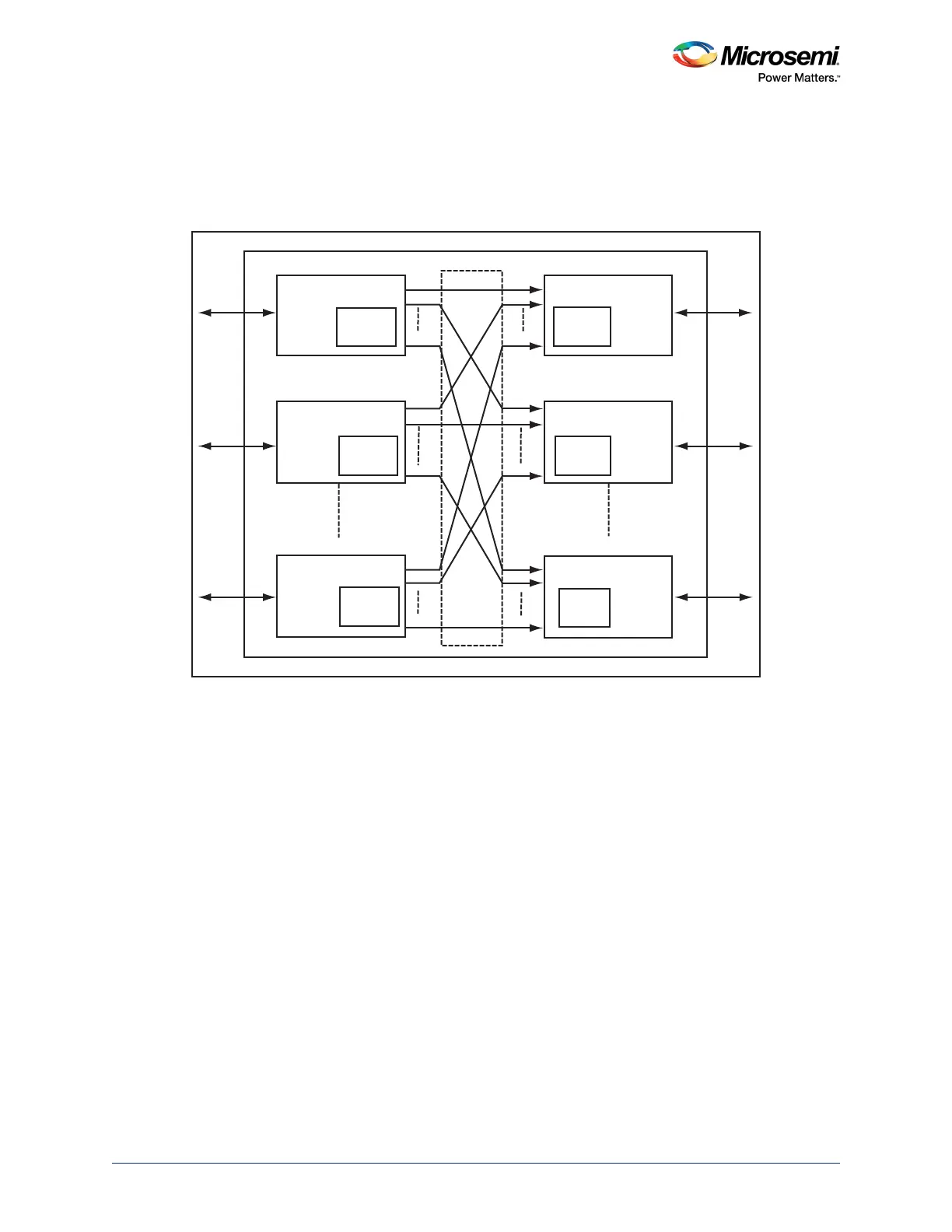

Figure 102 • Master Stage and Slave Stage Interconnection

To reduce the load on the AHB bus matrix, some of the low-performance peripherals are connected

through the synchronous AHB-to-AHB bridge with an address decoder. The AHB bus matrix is

constructed of combinatorial logic, except for the AHB-to-AHB bridge, which inserts a one-cycle delay in

each direction.

Master Stage 0

Slave Stage 1

Slave Stage 6

Master Stage 9

Master Stage 1

Slave Stage 0

Address

Decoder

Slave

Arbiter

Slave

Arbiter

Slave

Arbiter

Address

Decoder

Address

Decoder

AHB

AHB

AHB

AHB

AHB

AHB

Loading...

Loading...