Cortex-M3 Processor (Reference Material)

UG0331 User Guide Revision 15.0 113

3.7.2.11 MemManage Fault Status Register

The flags in the MMFSR indicate the cause of memory access faults. The bit assignments are:

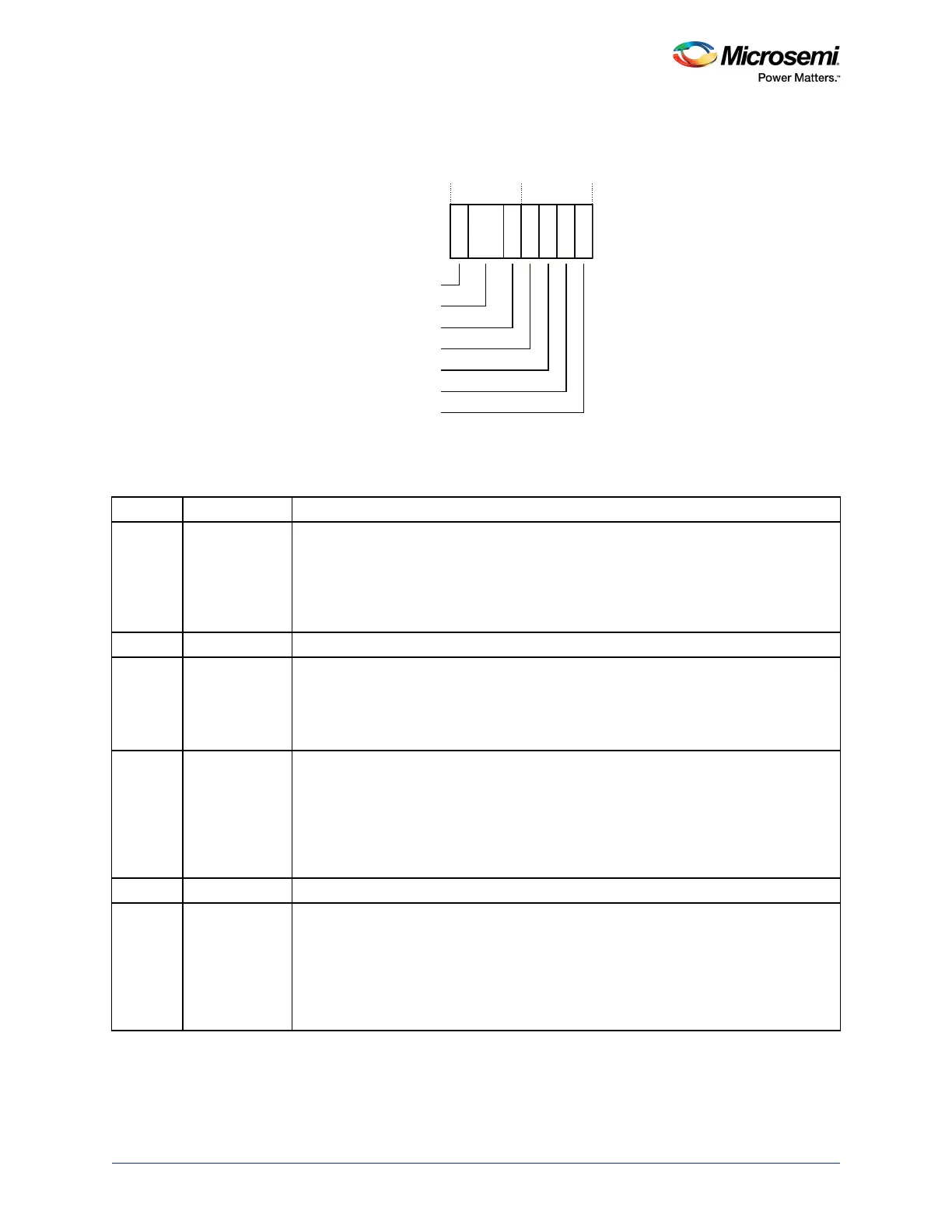

Figure 42 • MMFSR Bit Assignments

Table 64 • MMFSR Bit Assignments

Bits Name Function

[7] MMARVALID MemManage Fault Address Register (MMFAR) valid flag:

0: value in MMAR is not a valid fault address

1: MMAR holds a valid fault address.

If a MemManage fault occurs and is escalated to a HardFault because of priority, the

HardFault handler must set this bit to 0. This prevents problems on return to a stacked

active MemManage fault handler whose MMAR value has been overwritten.

[6:5] Reserved.

[4] MSTKERR MemManage fault on stacking for exception entry:

0: no stacking fault

1: stacking for an exception entry has caused one or more access violations.

When this bit is 1, the SP is still adjusted but the values in the context area on the stack

might be incorrect. The processor has not written a fault address to the MMAR.

[3] MUNSTKERR MemManage fault on unstacking for a return from exception:

0: no unstacking fault

1: unstack for an exception return has caused one or more access violations.

This fault is chained to the handler. This means that when this bit is 1, the original return

stack is still present. The processor has not adjusted the SP from the failing return, and

has not performed a new save. The processor has not written a fault address to the

MMAR.

[2] Reserved

[1] DACCVIOL Data access violation flag:

0: no data access violation fault

1: the processor attempted a load or store at a location that does not permit the

operation.

When this bit is 1, the PC value stacked for the exception return points to the faulting

instruction. The processor has loaded the MMAR with the address of the attempted

access.

MMARVALID

MSTKERR

MUNSTKERR

DACCVIOL

IACCVIOL

Reserved

Reserved

76543210

Loading...

Loading...